【数字IC】深入浅出理解UART协议

- 什么是UART?

- UART的帧格式

- 为什么UART通讯必须开始?

- 最基本形式的UART数据

- 为什么UART数据比特变异?

- UART的波特率

- 什么是波特率

- 如何换算波特率

- 波特的速率是否与采样频率成正比?

- 各级工程师的各种UART协议问题

- 嵌入式开发人员

- 电路设计人员

- IC设计人员

- 写在最后

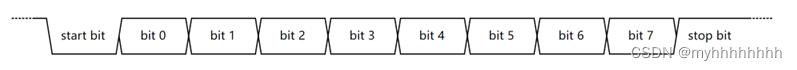

- 如果没有默认传输数据,则水平被设定为高。

- 当信号降低时,传输线上的水平下降,数据传输开始。

- 数据位数,可能是5、6、7或8,作为起点。

- UART 的“ 核查位置” 与“ 数据位” 相近, 使用奇特的检查技术, 视参数而定, 它可以存在, 也不可能存在 。

- UART在数据位数(无校准)和校准位数(有校准位数)之后,使用中继站作为停止信号,以传递1-2比逻辑“1”高度。

- Verilog UART 从地面起设计

- 固定的UART接收机/接收机;

- 支持5-8位数数据空格、1.5位数中途停留和可能关闭的奇迹校准空格。

- 能够识别框架格式错误和玩偶检查结果错误;

- 波特率可调;

收集并集中关注作者,以接收最新资料

最后更新:2022-05-10 19:38:20 手机定位技术交流文章

彻底理解UART协议

什么是UART?

UART的全名是世界非同步传送器。

广泛使用UART作为普遍接口协议,在各种MCU和SOC设备上广泛应用UART,反映了全球的互操作性。

“不需额外时钟线的同步数据传输”显示了非同步异质性,只要信号下降,数据就可以在其中传递,但其他通信协议,如AMBA,则需要引入时钟信号才能运行。

接收者/传输者:发送者认识到数据发送者和数据接收者分别要求建造接收者和传输者。

UART的帧格式

UART框架由起始、数据、检查和停止组成,数据按地点传送,如下图所示。

为什么UART通讯必须开始?

因为UART缺乏控制线通知接收者何时可获得数据,需要一些手段,在传输UART数据时,只有一根线,因此,在提供数据之前,作为数据交付的第一个标志,提供了符合逻辑的“0”。接收方在空闲时,当发现缺电时_ 其他协调员

在UART的具体设计中,可以提及作者关于如何探测低水平电极并利用低水平电极探测电路的著作:

Verilog的边缘探测(上、下、下、双边)

我们显然在使用电路上的滴子

最基本形式的UART数据

Verilog还可以利用提交人先前关于Verilog案件应如何构建的文章。

为什么UART数据比特变异?

由于UART是一种低速公交车,其后每次放电都需要大量时间(视传输率而定),视传输数据的特点而定,可采用替代位宽来缩短传输时间。

UART的波特率

在对UART传输协议进行更高层次的审查时,如果嵌入开发者的角度与嵌入开发者的角度相同,则与嵌入开发者的角度相同。我们会发现,在使用特定的UART安排之前,港口利率必须在发货人和接收端之间保持同步。这保证了在发射端收集的数据在接收端准确收集。标准港口费率为300。1200,2400,9600,19200,38400,115200,这些数字意味着什么?别着急,我们现在就开始吧

什么是波特率

波特费率是每秒通知的地点数目。如果我们的世界时钟频率是100兆赫港口利率已定为9600。因此,UART传输协议可以每秒发送9 600位数据。换句话说,发送一小部分所需时间约为10 609(ns)/9/9600=104166(ns)。

如何换算波特率

书接上文,如果东西是100兆赫,它就是100兆赫。这意味着我们的时钟周期为10毫秒。因此,我们可以在10,416钟周期中发送1位数据。要处理100兆赫时钟,我们需要一个10416大小的亚频电路。因此,在开发UART的同时,为了根据港口速率管理全时钟,我们必须使用亚频电路。数据按照频率之后的时钟节奏提供和接收。

同样,我们也可以参照作者前一份文件,学习如何创建频率电路。

Verilog的奇数分数对称类比。

韦里洛格的偶频核核糖酸

维利洛格的半因果自相残杀歌曲

Verilog 中的十进制小数量和谜题设计模拟

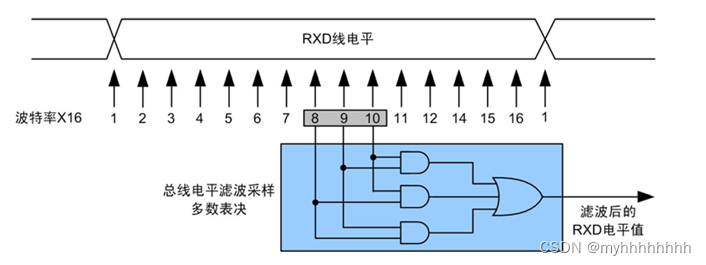

波特的速率是否与采样频率成正比?

您真的希望读者考虑一下吗? 如前所述,因为港口费率和取样频率表明,9 600个港口费率相当于9 600个样品的接收端和9 600比特发射端的发射端。

答案其实是否定的

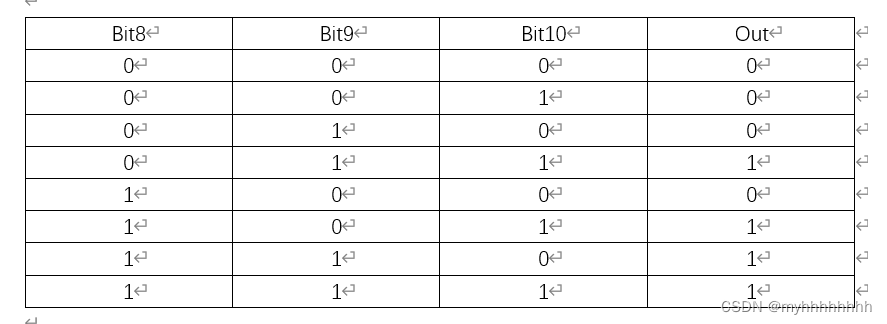

这是因为:在数据传输期间,信号可能因振动而中断(例如,与近端干扰的电磁兼容性设计)。如果接收端只使用其中的一个信号作为样本,因此,可以想象,它抽取了不正确的数据。因此,当对接收端进行抽样检查时,通常都要采样多次,然后,通过处理,我们获得正确的数据。比如说,以多数票表决,我们可以在接收端进行多次抽样。得到准确值,以下图像描述了16次抽样的多数投票电路的结构及其实际价值表。

查看实际表格,我们可以看到多数表决功能(即输出为1的两位和输出为0的两位)。

各级工程师的各种UART协议问题

嵌入式开发人员

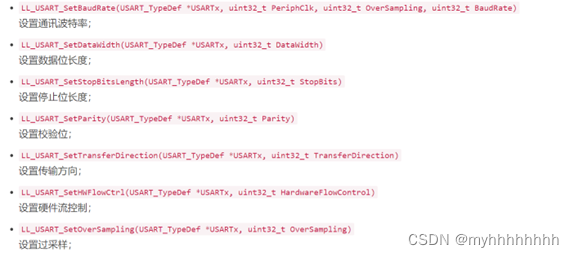

对于嵌入开发者,在使用 UART 时,在对图书馆功能进行包装时,必须使用以下参数:端口速率、长度、校准等。

电路设计人员

如果是电路设计工程师必须考虑UART的电力特性。例如,在RS232 UART协议中,** “逻辑”1是3-V-15V。+315V** 逻辑为 0。最初的15-V至15-V电压范围必须与MCU电压区别开来。第二,RS-232中的UART和RS-485中的UART具有不同的特点。在电路一级,我们需要RS-232型平板电路等结构的协助。

IC设计人员

此外,对于IC设计工程师,利用硬件说明语言,考虑嵌入式开发所需的港口费率。数据位数,奇偶校验,采样频率,这个项目是我们人权观察社特别报道的一部分。还有一个可编程的登记册这是跨越硬件和软件之间鸿沟的唯一方法。提交人对IC设计比IC设计更熟悉。因此,这项工作大部分是从IC设计的角度撰写的。

写在最后

在下一篇文章中,我们将利用Verilog系统从头开始建造UART系统,并进行不充分的验证,UART系统尤其符合以下参数:

本文由 在线网速测试 整理编辑,转载请注明出处。