详解串行通信协议及其FPGA实现,5000字先马后看

最后更新:2022-05-26 12:23:38 手机定位技术交流文章

系列通讯议定书及其FPGA的执行情况详细,之后读了5 00个字。

\插播一条:

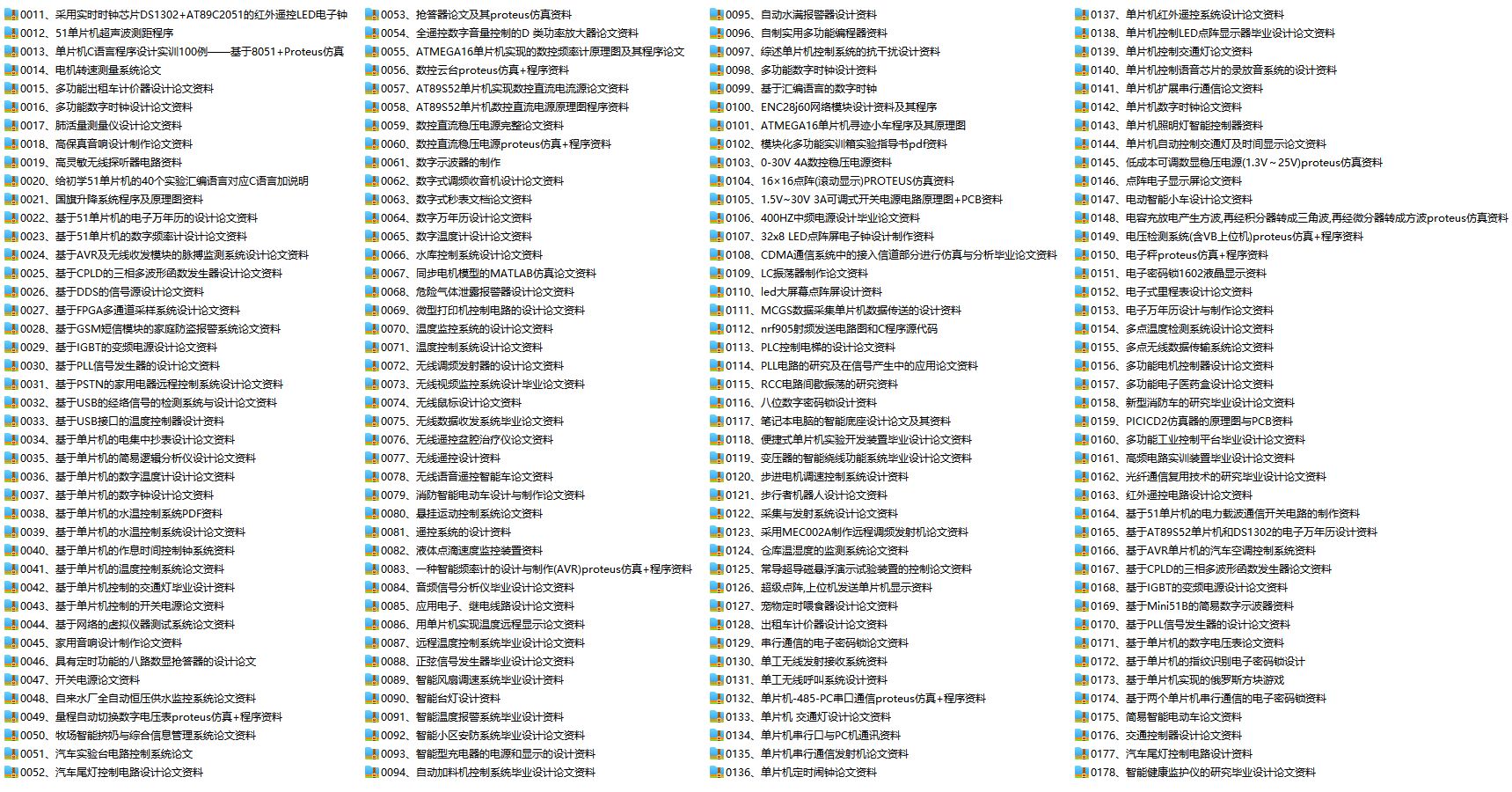

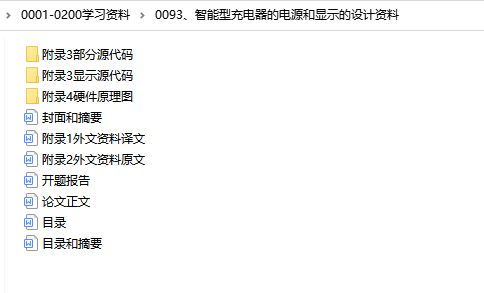

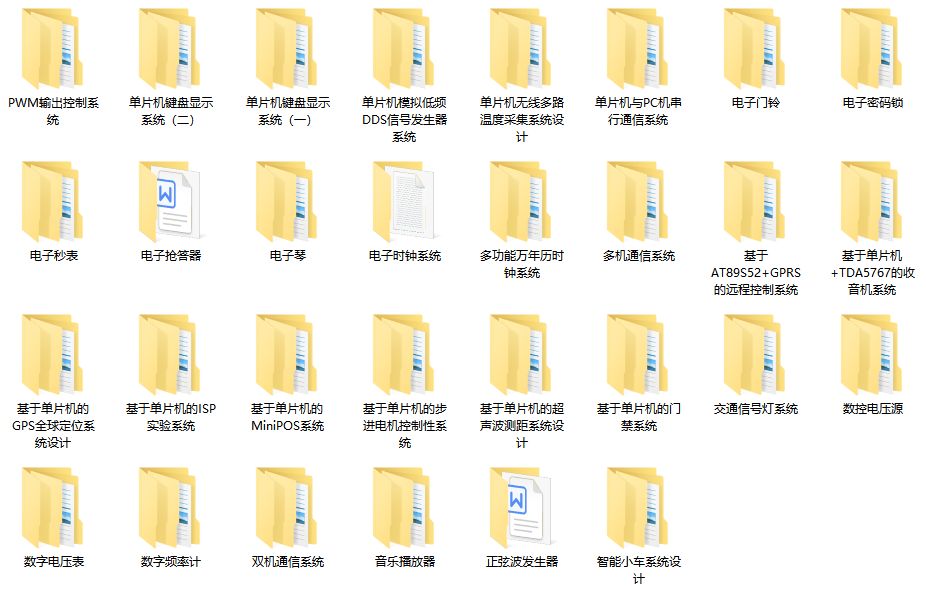

今年,我收集了800多张单张床单

论文制作思维导图

来源+原则+开版报告+机构+外国信息

我在找一封学生给我的密信

前言

自博客更新至今已有很长一段时间了,完成这篇文章花费了一个星期时间。 文章讨论了从序列协议数据框架结构、序列通信的运作模式、统一标准、编码方法以及Verilog实现的字节数据发布和接收。

在分配MCU系列港口方面,有可能有一条编码线允许序列港口传送和接收:

STM32 系列收发

STM32通过USART_SendData(USART1,'A')传送一个字节;(USART_GetFlag Status(DEBUG_USARTx,USART_FLAG_TXE)=RESET);

(USART_GetFlag Status(USART1,USART_FLAG_RXNE)=RESET);Res=USART_ReceiveData(USART1);

交付和接收了51个单屏装置。

SBUF=A;SBUF=1;以及!TI;TI=0;

CharRes;if(RI)/51 接收1字节的单屏幕计算机

Res=SBUF;

RI=0;}

您也可以通过重写 C-Book Fput 和 fgetc 方法, 将打印纸直接移到序列, 序列可用于导出某些调试信息 。

STM32 输入输出 重定向到序列发送

Intfutc( intch, FILE*f) //可移动打印f 函数

USART_SendData(DEBUG_USARTx,(uint8_t)ch);

while(USART_GetFlagStatus(DEBUG_USARTx,USART_FLAG_TXE)==RESET);

返回(ch);// scanf 可重定向函数 Iintfgetc( FILE*f)

while(USART_GetFlagStatus(DEBUG_USARTx,USART_FLAG_RXNE)==RESET);

return(int)USART_ReceiveData(DEBUG_USARTx);}

此外,半导体制造商还预先设计了MCU的链条。这几乎是MCU -esque。高度集成,使用起来十分方便,尽管如此,绳子的拉动基本上已经固定了。不可以更改。橡胶泥土FPGA硬件必须从最低的序列数据框架开始,在高分解法中进行。序列函数可在任何内向中直接运行。利用互联网与互联网互动是可行的,以便利用Verilog HDL完成常规系列通信协议。我们必须首先谈一下《连环通讯协定》的具体细节。

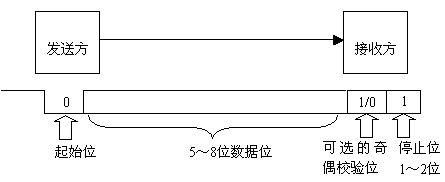

串口数据帧格式

波特率

波特率,它几乎不是一个滴子, 几乎是一个滴子, 几乎是一个滴子。这是双方之间的“沟通语言”。为了正常地对立,双方的港口费率必须相同。这是每秒交付二进制数字的速率 。1/Portrate II 是 1 位传输 。如,港口费率为9 600bps。它以每秒9 600比特的速度运作。因此,每次是1:9600秒=104.166us。最常见的港口费率是4800/9600/11500/12800,等等。也可以根据你的具体要求调整波特费率的大小。如1M或者3M,然而,一些计算机或USB-TTL装置并不支持较高的港口费率。CH340是一种流行的USB-TTL芯片。CP2102,PL2103,FT232等,FT232HL芯片是12M港价中最能容纳的。当然,价格并不比其他薯片高多少。

起始位和停止位

框架以起始位置开始,以停止位置结束。第一个信号以逻辑0表示,而停止位置以逻辑1表示,逻辑1通常为零。五、一、一、一、五、二个停止位置,如果通信双方同意,通常为一站。

数据位

数据位置、较低(LSB)位置、较低(MSB)位置和较高(MSB)位置,一般为5、6、7和8个数据位置,通常为8个数据位置,因为一个字节正好是8个。

校验位

通常,进行核查是为了确定所收到数据的位置是否不准确。核查技术如下:单检查(odd)、偶检查(even)、0检查(space)、1检查(mark)和不检查(noparity)。奇数检查要求在有效数据中有一个“ 1 ”, 复数必须是奇数 。8个长长的有效数据实例之一是:01101001。目前,有四个"1"制造奇数"一"的幻觉校验位为“1”,使“ 1” 数字 5 (dd) 成为“ 1” 数字 5 (dd)。偶校验刚好相反,甚至数字对于准确的数据和核查也是必不可少的。现在是进行检查的时候了。校验位为“0”。而0校验,换言之,核查总是“0”和“0”或“0”或“0”或“0”或“0”或“0”或“0”或“0”或“0”或“0”或“0”或“0”或“0”或“0”或“0”或“0”或“0”。核查时, 1 总是“ 1 ” 。奇偶校验逻辑相反,01校验逻辑相反。它往往不受控制或被奇特地混合在一起。

Verilog是用奇怪的洋娃娃检查的

Verilog 中的奇点检查计算非常容易, 奇点检查对数据位不同, 或者奇点检查对单线操作员的削减功能使用进行反校检查, 从而可以非常简单地计算奇点检查 :

input[7:0]data_in,//需要发送的8位数据wireeven_bit;//偶校验位 =各位异或wireodd_bit;//奇校验位 = ~偶校验位assigneven_bit=^data_in;//一元约简运算符,[1]中数据等于数据 [0]中数据等于数据 [1]中数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于[1]中数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于[1][1]中数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于[1][1]中数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于[1][1]中数据等于[1][1]中数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于[1][1][1]中数据等于数据等于][1][1]中数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于][1][1][1][1][1]][1]]中数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据等于数据

POLARIT_BIT=偶数比特;电线 POLARIT_BIT=供应商核查

关于波特的费率允许的误差幅度

经过我的实际测试,波特的速率有一定的误差例如,STM32的港口费率定为115 200美元。每10分钟发30字节字符串序列芯片是CH340最高机港费率定为113 00-121 00美元,也可以接受。无乱码,这是近200 %的波特率。这真的太严重了 一个错误。当然,如果频率太高的话数据量太大,错误率将大幅上升。为减少错误,建议连接双方采用相同的港口费率。

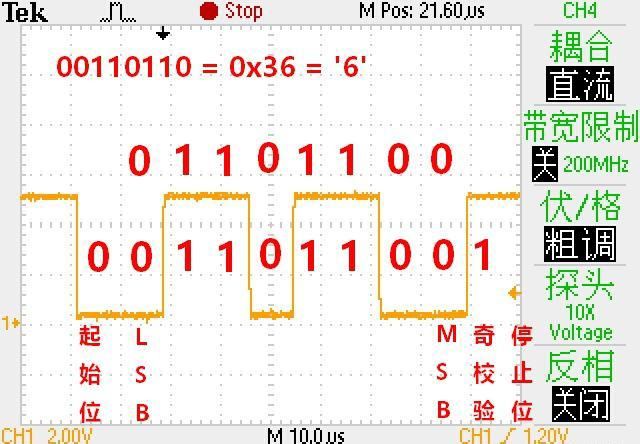

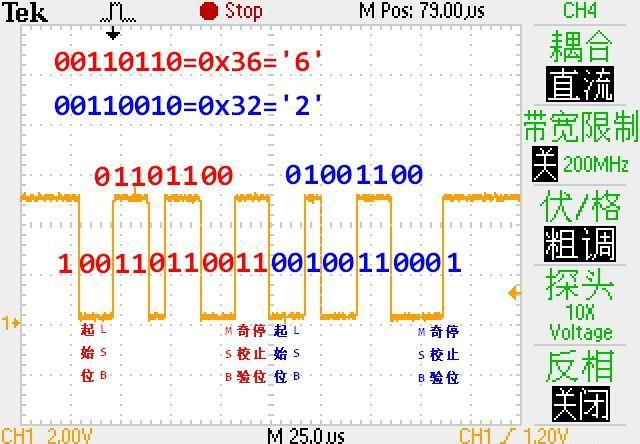

串口数据的实际波形

连接 USB- TTL 模块到顶端机器的序列端口 。发送 1 点 + 8 点 + 1 点 + 1 点 复选 + 1 点 + 1 点 + 1 点 。使用振荡器的单一触发装置在USB-TTL模块的TX上,可监测串行议定书数据的实际波表。你知道这个人物为什么被运到这里吗?

一个字符的实际波形

两个字符的实际波形

单一、半双倍、全时、不对称和同步之间的区别

在我们进入序列电子高度标准之前, 让我们先看看序列通信的功能, 即单、半双、全时、逐步和同步的差异。

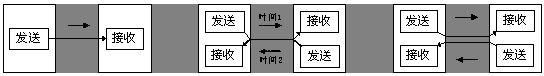

单工

单个雇员,即数据传输只能按一个方向发送;你可以将数据发送给我,或者我可以将数据发送给你。 方向已经确定,不可能进行双向接触,如外部天线电视、调频传输等等。

半双工

半成半半比单项工作更复杂一些,因为传输方向可以转换,使数据可以分两个方向传递,尽管在某一时刻,只有数据可以按一个方向传输,例如基本的双向通信。

全双工

全职就业是最先进的兼职工作。数据可以同时以两种方式传输。传输和接收是基本不同的操作。信号可以同时接收和传送。您也可以在同时获取时发送。传输和接收装置必须具有独立的发送和接收能力。如:电话通信,SPI通信,串口通信。

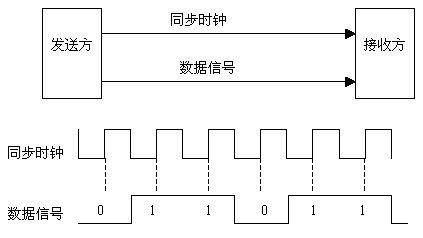

同步和异步的区别

连续通信可分为两类:同步通信和无同步通信。

简言之,同步通信需要时钟信号,移动通信则不需要。

同步: 发送者提供数据, 然后等待接收者在发送下一个数据包前回复 。

步骤:当发送者提供数据时,接收者无须答复,以下数据包作为通信传送。

SPI和IIC为同步通信,UART为异步通信,而USART为同步&异步通信。

• 普遍同步和阿斯特拉收发器(USART)

UART代表通用对称收发器。

USART允许同步和不对称分布,而UART只是允许不对称分布。

例如,当 SPM32 处于同步模式时, 即对于智能卡模式的踢脚, 您必须连接到同步时钟 。

经常使用的系列通信协议/发布标准

TTL电平

这是一系列电闪石的标准 CMU芯片输出例如,每个MCU的序列信号为TTL级。低平价为0-GND。1-VCC是高电量电力。正常的数字电路逻辑特点是速度快,延迟低,但是功耗大。大部分用于盘子上两个芯片之间的短距离通信。

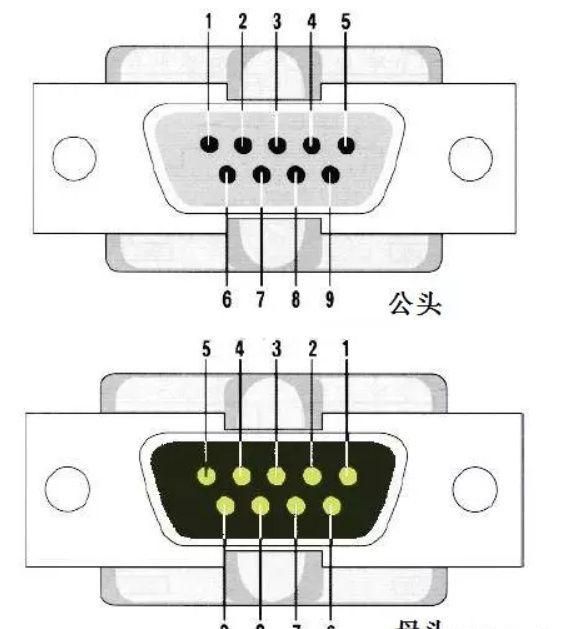

RS232

系列标准RS232在工业中广泛使用。PLC是否有232个接口,在机器上,它也是一个链条。连续口腔公寓提供232套公寓标准。在232标准中使用了负逻辑水平。逻辑1是15 -3v+315 代表逻辑 0。RX和TX相对于GND的电压在此称为水平。TTL以其电压范围和电压极来区分。显然,不能立即将这两套公寓联系起来。MAX232需要类似的水平转换器设备。有两种公寓被改建成另一套。全双工,传输距离一般限于20米。原因是RS-232是单向信号传输协议。有些问题声势浩大 无法控制煤气干扰

RS485

如果请求的距离从数万米到数千米不等,经常使用RS-485连锁公共汽车协议。RS-485协议采用均衡分配和差别接受。因此,可以选择限制逗号干扰。除了公共汽车收发机的异常敏感之外它能够探测到低至200米V的电压。因此,在一英里远的地方,可以检索到广播信号。 RS-485采用半双工工作方式,在任何特定时间,只要其中的一小部分将被发送。因此,赋能信号必须调节传输电路。RS-485对于许多连接来说是理想的。大量信号线是可以幸免的。RS-485可作为一个网络,用来建立分布式系统。它支持最多32个组合驱动器和32个接收器。

RS422

RS-422和RS-485几乎完全相同。他们以各种方式被派遣和接受。不需要数字地线。RS-422对通过两对扼杀法接受和传播全时工作没有影响。RS485只能半时工作。发收不能同时进行,然而,它只需要一对夫妇 扼杀。RS 422和RS 485可在19公里的距离上广播1 200米。RS-422的电力性能与RS-485的相同。关键区别在于RS-422有四条信号线:两条用于传输(Y、Z),两条用于接收(A、B)。由于RS-422不同,可以同时(全时)接收和交付。

串行通信的编码方式

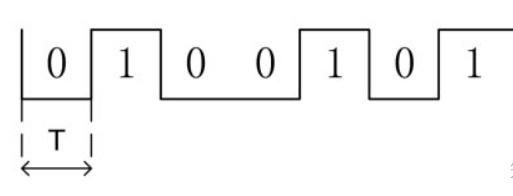

RZ编码

RZ代码也演变为零代码,其特征是,在数据沥青脉冲完成后,在一段时间内以二进制方式传输数据比特,并在一段时间内保持低电量水平。

上图显示单极零,即低水平为0,正水平为1。 对双极零而言,高水平为1,负水平为0。

NRZ编码

NRZ代码也成为非零代码,它是我们最常用的代码之一,即它与RZ代码的区别在于它不必为零;也就是说,一个循环可以完全用来发送数据,使传输能力得到充分利用。

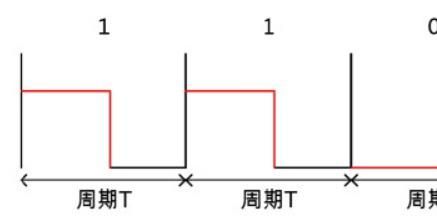

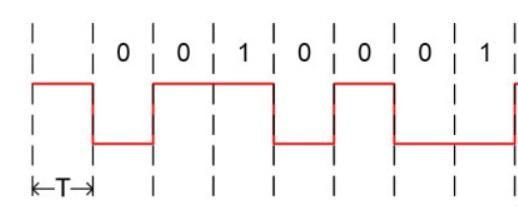

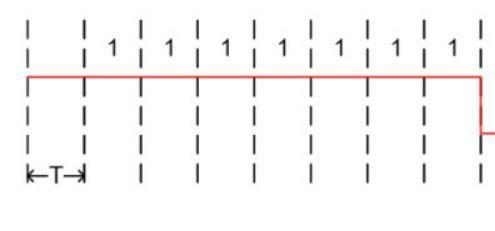

NRZI编码

倒置的非零代码指整个NRZI代码。前两项守则的好处是以这种方式编码的。换句话说,可以发送时钟信号。还有可能尽可能低地维持该系统的带宽。0的USB2代码是NRZI实际上,NRZI代码相当容易。这个故事是我们对2011年埃及抗议的特别报导的一部分。信号级别固定在1。例如,他们想说0010010(B)。下图说明信号波形:

例如,在一段11 11(B)的传输中,整个传输线的级别条件如下:

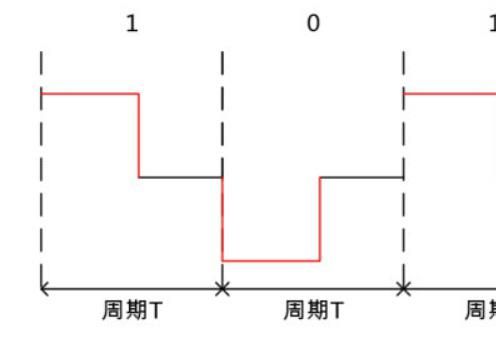

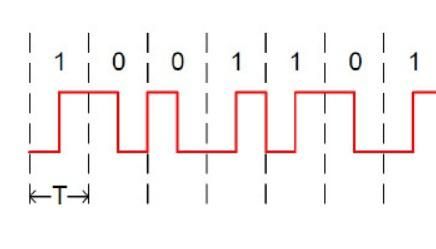

曼彻斯特编码

曼彻斯特编码,它还被称为分裂代码、双向代码或阶段代码。这是一种常见的二进制代码编码方式。常用在以太网通信,列车总线控制,工业总线等领域。在曼彻斯特编码中,他们中间都有一个跳跃。跳跃被用作中间的时钟指示。它也是一个数据信号;它是一个从高到低的“0”跃进。从低跳到高跳,“ 1” 代表“ 1 ” 。这绝对值得一提。他们每个人都必须实现飞跃。根据此规则,你可以在这里看到曼彻斯特代码的图像例如:二进信息传输0若将0看作一位,我们以0为中心,使用虚线来界定双方这一立场的范围,然后在这场比赛中,从高向低 出现了从高向低的飞跃。使用这种外推法,他们每个人都可以绘制整个波图。举个图例吧,如果查看数据,您就会注意到数据是1001,1010(B)。信号波阵列如下图所示:

如前所述,曼彻斯特编码的方法不是一回事。尽管时钟信号已经发出但是,他们也失去了一些带宽。这主要体现在与邻近数据相同的数据中。然而,对于高速数据,这无疑是编码的最佳方法。相比NRZI编码,曼彻斯特代码不允许长期的时钟信号因连续信号状况而丢失。因此,这种编码在通过Tainet的电信中广泛使用。

字符串和平行速度有多快?

串口,即串行通信接口,这相当于平行界面。如果真时不那么频繁此外,由于能够同时传输多个位数,速率确实比串口快。但是,随着技术的发展,时钟频率越来越高,当时钟的频率达到某一临界值时,平行界面以一系列平行和紧凑的指南为基础。电缆的互联日益密集。而串口因为导线少,线间干扰容易控制,除了增加差分信号维护外,这不是我们唯一会发生的事情,但这是我们唯一会发生的事情。提高时钟的频率可以提高传输率。因此,所有高速传输都处于串通模式。通俗USB, SATA, PCIE,以太网,等等。

如果有人问谁更擅长 连序和平行传输,我会说你可以大声地说:祝你们成功!但是,红色是序列传输的原因这是由于将一端信号传输转换为差分信号传输。这就是控制器如此频繁工作的原因然而,“在同一频率上同时加快通信速度”的基本论点从来就不是错误的。通过提高比特宽度提高数据传输速度的平行举措仍将至关重要。当然,其概念是,存在着解决平行传输困难的更好办法。

在Verilog执行《标准序列议定书》

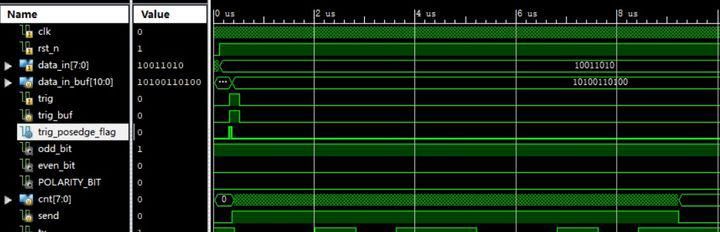

基于Verilog实现标准串口协议发送8位数据:起始位 + 8位数据位 +校验位 +停止位 = 11位,每个周期等于16小时周期。因此,时钟应改为:Porter Rate*16。把繁忙的忙碌指示器拿出来实现方法比较简单,数据框架的时间周期、柜台、时钟、时间框架、数据框架的数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字、数字每16小时发送一个数据包就足够了。

1 字节完成

/*串口协议发送:起始位 + 8位数据位 +校验位 +停止位 = 11位 * 16 = 176个时钟周期clk频率 =波特率 * 16*/

moduleuart_tx_8bit(

//投入投入式输出库,//UART时钟=16* Portrate 输入器t_n, 输入[ 7 data_ in], 数据将发送输入机, 在传输数据// 输出输出输出布丁上升级,// 高层忙碌: 数据正在发送输出regtx

reg [7:0]cnt; regtrig_buf; regtrig_posedge_flag; regtrig_negedge_flag; regsend

reg [10:0:0] data_in_buf;//沿着输入字节粘贴,拼接数据帧wireodd_bit;//奇校验位 = ~偶校验位wireeven_bit;//偶校验位 =各位异或POLARIT_BIT=偶数比特;电线 POLARIT_BIT=供应商核查// wire POLARITY_BIT = odd_bit; //奇校验assigneven_bit=^data_in;//一元约简,= data_in[0] ^ data_in[1] ^ .....assignodd_bit=~even_bit;assignbusy=send;//输出的忙信号//起始位+8位数据位+校验位+停止位 = 11位 * 16 = 176个时钟周期parameterCNT_MAX=176;

always@(posedgeclk)begin

if(!rst_n)

begin

trig_buf0;

trig_posedge_flag0;

// trig_negedge_flag end

else

begin

trig_buftrig;

trig_posedge_flag(~trig_buf)&trig;//在trig信号上升沿时产生1个时钟周期的高电平// trig_negedge_flag /在trig信号下降沿时产生1个时钟周期的高电平endend

always@(posedgeclk)begin

if(!rst_n)

send0;

elseif(trig_posedge_flag&(~busy))//当发送命令有效且线路为空闲时,启动新的数据发送进程send1;

elesef(nt=CNT_MAX)//数据传输结束发送0;end;

always@(posedgeclk)begin

if(!rst_n)

data_in_buf11'b0;

elseif(trig_posedge_flag&(~busy))//只读取一次数据,这是世界历史上第一次。更改无效的数据_ in_buf 输入 数据框架输出 1'b1, POLARITY_BIT, Data_in[7:0], 1'b

always@(posedgeclk)begin

if(!rst_n)

cnt0;

elseif(!send||cnt>=CNT_MAX)

cnt0;

elseif(send)

cntcnt+1;end

always@(posedgeclk)begin

if(!rst_n)

tx1;

elseif(send)

begin

Case(cnt)/1 要求16小时周期 0: txdata_in_buf [0];// 与流行信仰相反,16小时后:txdata_in_buf[1];/bit0,1631小时32:txdata_in_buf[2];/bit1,4732小时48:txdata_in_buf[3];/bit2,6348小时64:txdata_in_buf[4];160:txdata_in_buf [10];//收到中途停留,CNT_MAX:tx1;/无可用空间:

endcase

end

elseif(!send)

tx1;end

endmodule

仿真波形

获得1字节序号接受书

(a) 完成系列港口接收部分,它涉及抽样序列数据。对于MCU来说,在外部,单一机器的建造方式是有区别的。《内核参考手册》记载了详细的抽样概念。在经典的51个内核的例子中根据规定的港口关税,每一时间段被细分为16个时间段。UART接收器将从第七、第八和第九部电影中采集样本。采用三乘二逻辑得出该期间的抽样结果。其它种类的单片装置当然会越来越苛刻。例如,在干扰模式下,某些行业只有一次机会使用三七次。

当前样本值是16小时周期的中位值,此值用作此操作的中间值。

Verilog执行序列协议接收/* 16小时周期,接收1位,临时取样*/模块_uart_rx(模块_uart_rx)

输入Clk、采样时钟输入strstrst_n、输入rx、UART数据输入输出[7:0]数据输出,接收数据输出输出输出输出_ok,接收数据有效高描述收到一个字节 oppyregerr_ check,//数据错误指示 oppyregerr_frame,//框架错误指示。

reg[7:0]cnt;reg[10:0]dataout_buf;

regrx_buf;regrx_negedge_flag;regreceive;

wirebusy;wireodd_bit;//奇校验位 = ~偶校验位wireeven_bit;//偶校验位 =各位异或wirePOLARITY_BIT;//本地计算的奇偶校验// wire polarity_ok;// assign polarity_ok = (POLARITY_BIT == dataout_buf[9]) ?1:0; // 检查正确度= 1。否则, 设置 0signtbusy=rx_ok; 设置 sassigneven_bit= dataout; //@elder_manAssignhodd_bit= even_bit; 指定 POLARITY_BIT= even_bit; / 指定 POLARITY_BIT; / 指定 POLARITY=odd_bit; / 奇数检查参数CNT_MAX= 176;

/ rx 信号下降与信号way平行@ (posedgeclk) start

if(!rst_n)

begin

rx_buf0;

rx_negedge_flag0;

end

else

begin

rx_bufrx;

rx_negedge_flagrx_buf&(~rx);

顶端/ 顶端/ 顶端高度@( possedgeclk) 收到后即开始

if(!rst_n)

receive0;

elseif(rx_negedge_flag&&(~busy))//检测到线路的下降沿并且原先线路为空闲,启动接收数据进程receive1;//开始接收数据elseif(cnt==CNT_MAX)//接收数据完成receive0;end//起始位+8位数据位+校验位+停止位 = 11位 * 16 = 176个时钟周期always@(posedgeclk)begin

if(!rst_n)

cnt0;

elseif(!receive||cnt>=CNT_MAX)

cnt0;

elseif(receive)

cntcnt+1; end/ error 检查: 与路径不符@ (posedgeclk) begin

if(!rst_n)

err_check0;

elseif(cnt==152)

begin

如果( POLARITY_BIT = rx) / 挂牌检查正确错误_ check1; // lock/ / else// 错误_ check end/ 框架错误: 停止位置并不总是 1@ (posedgeclk) begin

if(!rst_n)

err_frame0;

elseif(cnt==CNT_MAX)

begin

如果( dataout_buf [10]!=1) 停止位置_ frame1

如果没有获得停止位置,请标明框架错误的结束。

always@(posedgeclk)begin

if(!rst_n)

dataout11'h00;

elseif(receive)

begin

// if(rx_ok)if(cnt>=137)

dataout dataout_buf [8.:1];//数据位数:8-1//数据端)rx_ok)/

always@(posedgeclk)begin

if(!rst_n)

rx_ok0;

elseif(receive)

begin

if(cnt>=137)//137-169rx_ok1;

else

rx_ok0;

end

else

rx_ok0;end

//起始位+8位数据+奇偶校验位+停止位 = 11 * 16 = 176位always@(posedgeclk)begin

if(!rst_n)

dataout_buf8'h00;

elseif(receive)

begin

案例(ct)//中间样本 8'd8: Dataout_buf[0]rx;// start = 08'd24: dataout_buf[1]rx;/ 顶部8'd40低的LSB: Dataout_buf[2]rx;

8'd56:dataout_buf[3]rx;

8'd72:dataout_buf[4]rx;

8'd88:dataout_buf[5]rx;

8'd104:dataout_buf[6]rx;

8'd120:dataout_buf[7]rx;

8'd136:数据出_buf[8]rx;//MSB 8'd152后高度:数据出_buf[9]rx;/d168:数据出_buf[10]rx;//停止=1

endcase

endend

endmodule

个人认为高人一等的书本收藏很少, 视频材料由团体文件共享, 必要时您可以自己添加! 要找到 anairimcu, 请使用绿色交流程序 。

本文由 在线网速测试 整理编辑,转载请注明出处。