【FPGA】IIC协议的应用实现

- 一.协议介绍

- 1.IIC

- 2.SCCB

- 3.EEPROM

- 二.状态机分析

- 三.模块设计

最后更新:2022-06-16 11:01:42 手机定位技术交流文章

文章目录

一.协议介绍

1.IIC

IIC是一个由数据线SDA和时钟线SCL组成的双线串行总线,可以用于传输数据或接收数据,是半双重通信协议。

总线上的主设备和从一个设备到另一个设备的双向数据传输。

它通常用于与主机和接收机在少量数据和短的传输距离中通信。主机启动总线,并生成数据传输时钟,此时,任何接收数据的设备被认为是接收器。I2C设备通常使用与总线连接的泄漏结构,因此,I2C_SCL和I2C_SDA都必须与拖拉阻尼器连接,也正因此,当总线空闲时,两条线路处于高电位平衡,当任何连接到总线的设备输出低压水平时,都将使总线拉低。

总线上的每个设备可以是主设备或来自设备,每个设备都与一个唯一的地址(从12C设备数据手册中知道)相符,用于确定该设备与主设备之间通信的设备。

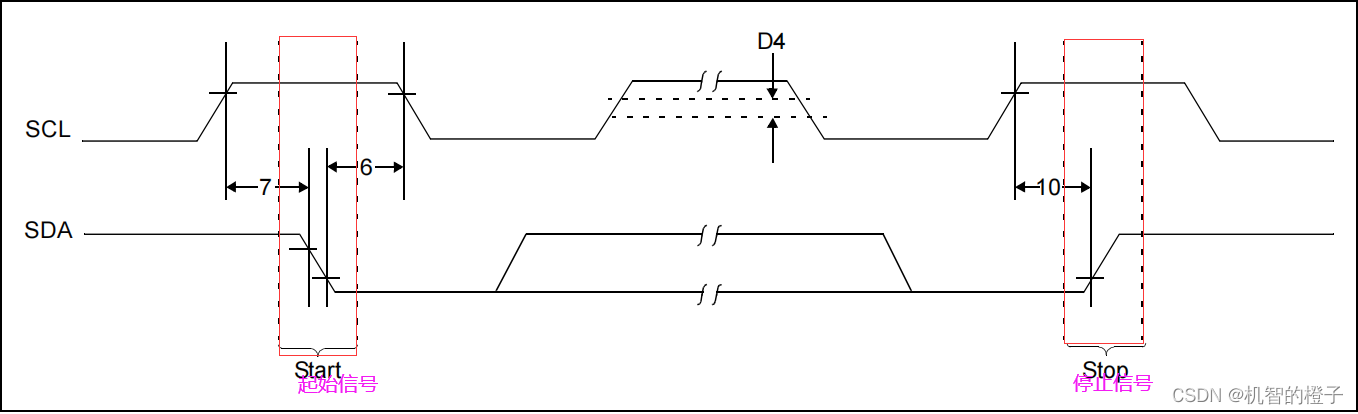

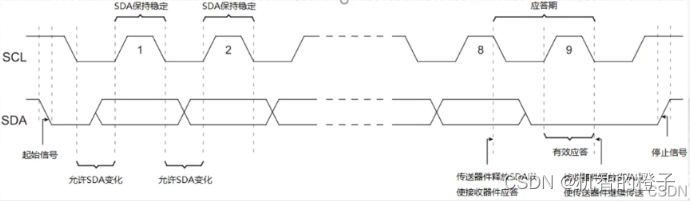

I2C时序

①空闲状态:

I2C总线的SDA和SCL两个信号线同时处于高电压状态,定义为总线的闲置状态。 此时,每个设备的输出级场效应管都处于关闭状态,即释放总线,两个信号线都拉高电压,拉高电平面。

②起始信号:

当SCL保持高电压水平时,SDA的电压水平会降低,称为I2C总线的初始信号,该信号指示数据传输L处理。 如果初始信号由主机启动,I2C总线必须在初始信号启动之前处于闲置状态。

③停止信号:

在SCL保持高电压水平时,SDA被释放并返回高电压水平,即I2C总线(英语:I2C bus)的停止信号,该信号表示数据传输的终止。

④数据传输:

在I2C总线上传输的每个数据都有时钟脉冲相对(或同步控制),即,在SCL串行时钟的同步下,每个数据在SDA上顺序传输。进行数据传送时,在SCL的高压平衡中,SDA的电压平衡必须稳定,只有在SCL水平较低时,仅允许在SDA上改变电机的状态。也就是说,在SCL的崛起之前,数据必须准备好。它必须稳定下来才能降下来。

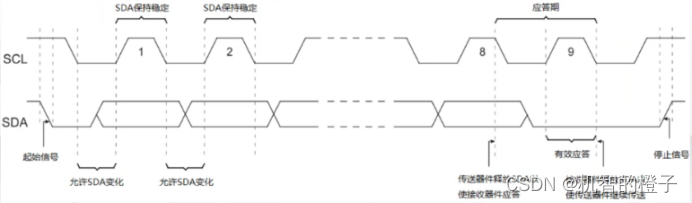

⑤应答信号:

12C总线的所有数据都以字节形式传输,发送端发送每个消息一个字符,SDA必须在第9个SCL脉冲中释放,接收器返回响应信号。反应信号通常是低的电流,它叫做效应反应(ACK),指示接收器成功接收节点;响应信号是高压正常,它叫做无反应状态(NACK),指示接收器未能接收字符串。ACK对反馈有效的响应的要求是:接收器在9时钟脉冲之前在低压平衡中降低SDA,同时确保时钟周期的高压水平保持低压水平。如果接收器是主控器,然后,当它收到最后一句话后,发送NACK信号,通知控制器数据传输的结束,并释放SDA线,向主控接收器发送停止信号。

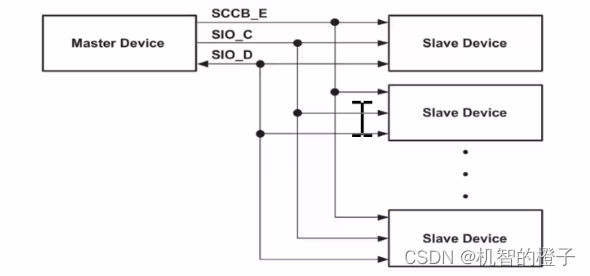

2.SCCB

SCCB ( Serial Camera Control Bus ) 是一种由 OmniVision 出版的串行相机控制总线协议.它相当于一个简单的I2C协议。SCCB有三条线和两条线,第三行是一个主机多服务器,两条线是一条主机,另一条线是另一条。

SCCB时序

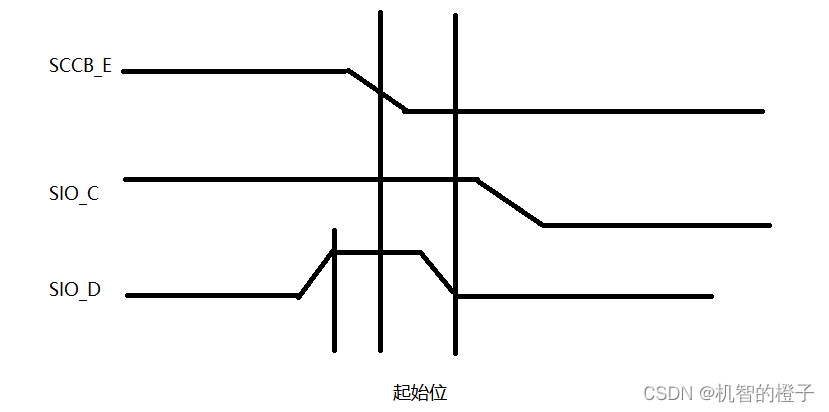

①起始信号:

当SCCB_E被拉出时,SIO_D在SIO_C期间被拉出为高压平衡,表示数据传输开始。

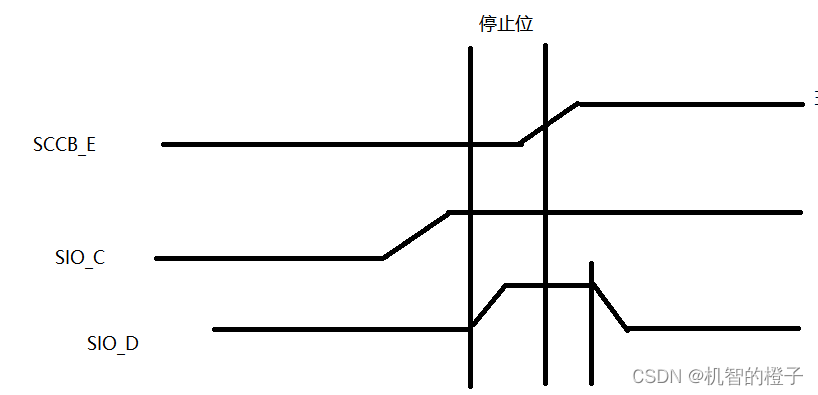

②停止信号:

当SCCB_E拖下时,SIO_D在SIO_C的高压平衡期间拖上,表示数据传输的结束。

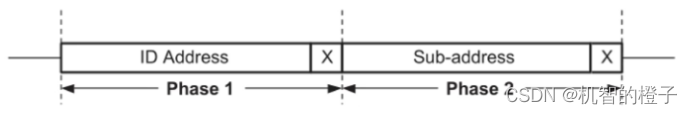

③数据传输:

在SCCB协议中,一个基本的传输单元叫做相.一个阶段总共包含9位元,前8比特为数据,它的响应信号ACK称为传输单元第9位,它被分为不关心和NA(No ACK)。护理节点由主机生成;NA节点由主机生成;由于SCCB不支持多字元读写,NA必须是一个高压水平。sCCB没有重复开始的概念,因此,在 SCCB阅读周期中,当主机发送卡中的内存地址时,必须发送巴士停站条件.否则,发送读取命令时,无法从机器产生不关心响应信号。

当写给接收机的数据被定义为写传输时,当从机器读取数据被定义为读取传输时,每个传输都有开始和停止;完整的数据传输由两个或三个阶段组成,每个阶段包含九位数据,其中8位是传输的数据,最低的位数有不同的值,取决于设备读写情况:

每个阶段包括:8位数据+不关心/NA

如果主机发送数据,即写字操作,则第9位为不关心;如果主机发送数据,即读字操作,则第9位为NA。

三相写传输:

ID添加器:指示机器的地址和读写控制;

子添加器:指示机器的服务器地址;

写数据:代表输入的1字节数据;

在三个阶段之后,最后的X是所有不关心的 bits。

两相写信传输:(读取数据的第一阶段)

ID 添加器: 指示机器的设备地址,并写入控制位置;

子添加器:指示机器的服务器地址;

两个阶段后最后的X是所有不关心的位子;

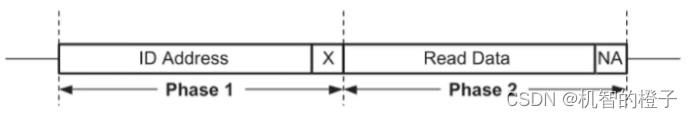

两阶段读取转移:(读取数据的第二阶段)

ID添加器:指示设备地址,并从机器读取控制位置;

读数据:表示从机器接收的数据;

X是所有不关心 bits; NA必须是1。

3.EEPROM

写操作时序

写操作,发起始位->写写控制字->接收ACK->写字节地址->接收ACK->写数据接收ACK->发停止位。

写控制字:

{7’b101000,1’b0}

单字母符号: 每次只写一个符号.

页面写作: 一个人可以同时写16个字符.

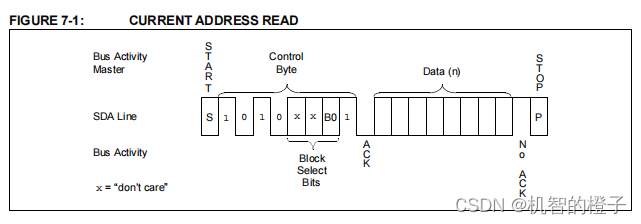

读操作时序

从当前地址读:

发起始位->写控制字->接收ACK->写读地址->接收读数据->发NACK->发停止位。

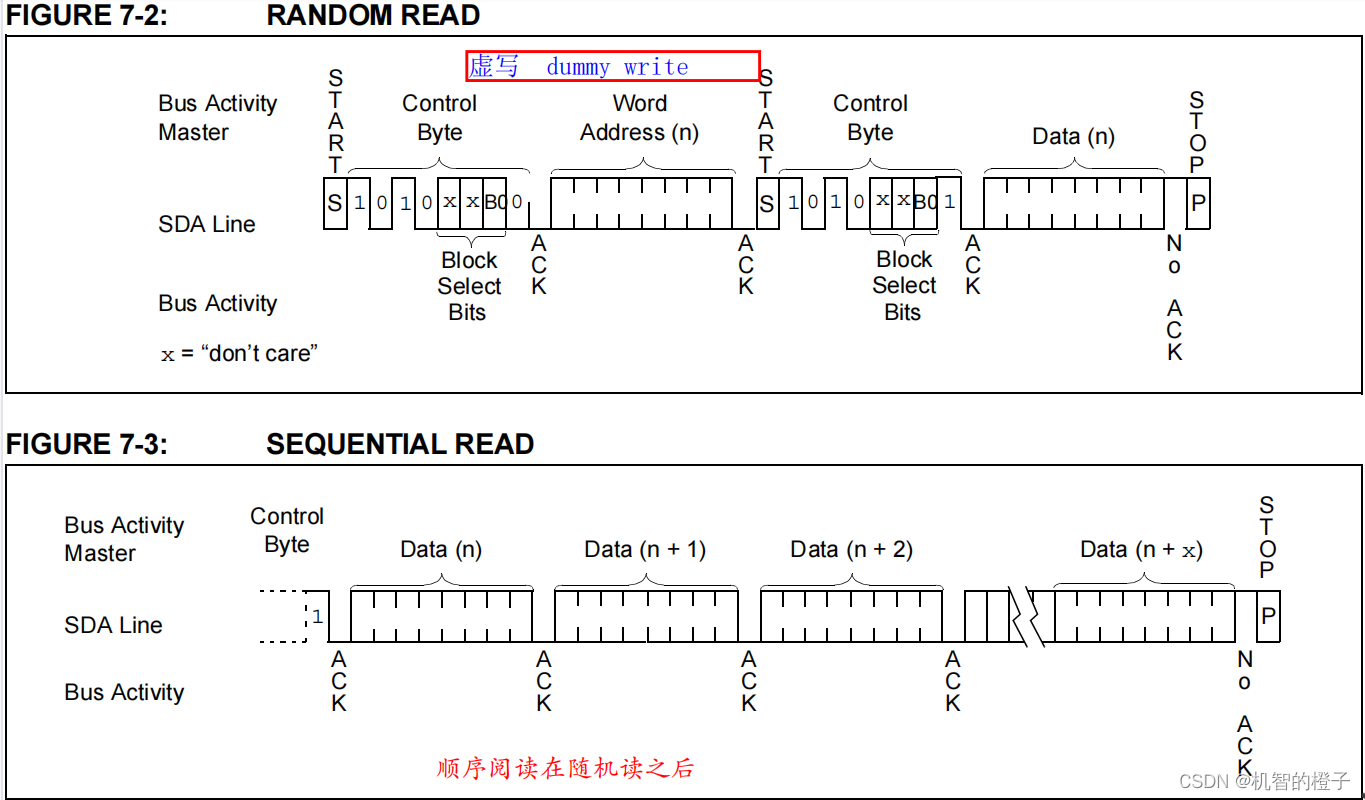

随机读:

随机读,发起始位->写控制字->写读地址->接收ACK->发起始位->写读控制字->接收读数据->发NACK->发停止位。

顺序读:

顺序读,发起始位->写控制字->写读地址->接收ACK->发起始位->写读控制字->接收读数据->发ACK->接收读数据->发NACK->发停止位。

二.状态机分析

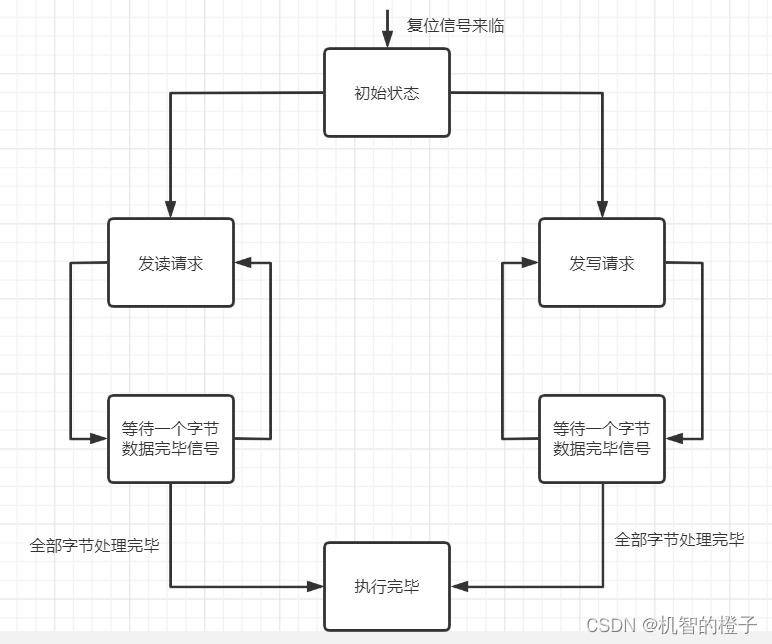

分析上述协议,我们发现,只有两种类型的读写操作用于EPROM数据,在分析时序可知,任何类型的阅读和写作模式,它可以按单位9位分开,只有两个类型的操作,用于9位数据,读写,因此,我们可以设计一个控制状态的机器,状态机器只关心操作的类型,9位数据如何处理并不重要。然后设计一个执行命令的状态机器,状态机器接收了以前状态机器的命令,在特定命令上执行特定操作。

状态机设计如下:

说明:

当读写数据信号临时输入时,状态机会跳跃发送写请求或发送读请求状态,然后开始发送相应的命令,以执行上述协议的状态机器。

控制状态机器进入发送写请求状态后,在第一行:向执行状态机发送请求信号,启动位置命令+写命令,注册表地址和读写控制单词;第二节点:向执行状态机发送请求信号,写命令,注册表地址;最后部分:向执行状态机发送请求信号,写命令+停止位命令,如果有一个中间节点:向执行状态机发送请求信号,写命令,数据。每个字节接收一个完整的信号,由执行状态机处理,作为终止符号。

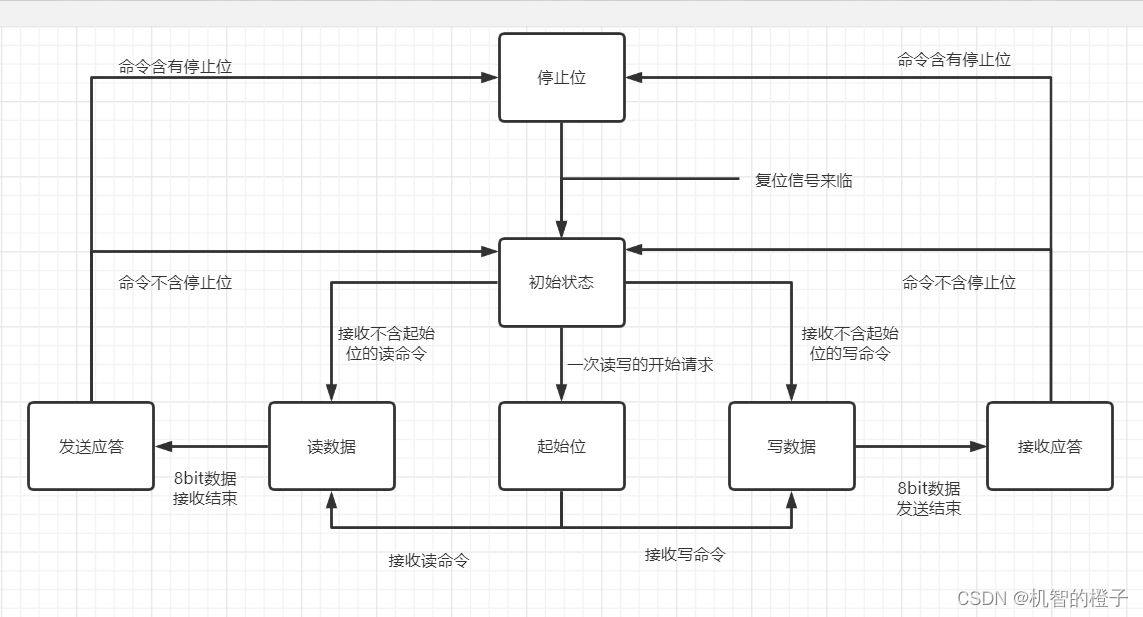

说明:

当状态在执行状态机重启动后处于初始状态时,当它接收读写信号时,状态机会跳到相应的状态来执行特定的数据操作。

当状态机收到写字请求时,第一个请求必须伴随初始位置命令,状态机器从初始状态到初始状态,在一个时钟周期内,时钟脉冲电压水平高时,状态机必须拉下sda总线,以产生启动位置条件,该周期结束,进入写数据状态,该状态为数据传输提供8个时钟周期,数据传输需要根据协议要求,在时钟周期脉冲低压平衡中改变数据,在高压平衡中保持稳定,八小时的周期之后,状态机器进入接收响应状态,如果接收命令不包含一个停止位命令或接收响应是一个非响应的返回初始状态,重新接受命令后直接从初始状态跳到写数据状态(当前是数据操作的一部分),其他操作都是相同的;如果接收命令包含停止位置命令,然后状态机器跳到停止状态,在那个状态的时钟方向循环中,在时钟脉冲高压平衡中拉高sda总线,产生停止位。至此,一次写操作结束。

三.模块设计

略

本文由 在线网速测试 整理编辑,转载请注明出处。