串口RS232的学习

最后更新:2022-06-22 00:20:33 手机定位技术交流文章

RS232通信协议的介绍

RS232是UART型,没有时钟线,只有两个数据线,rx和tx,每个宽1位,其中rx是接收数据的线,tx是发送数据的线。

2,Rx位宽为1位,而PC通过串行调试助理向FPGA发送8位数据,而FPGA通过Rx串行线接收数据,从最低位到最高位,最后将这些位数据集成到FPGA中的8位数据中。

3,tx比特宽为1比特,FPGA通过串行端口向PC发送8位数据,FPGA通过Tx线向PC发送8位数据,从最低到最高,最后,高级机器通过一个串行助理,按照RS232协议将这个单元数据位组装成8位数据位。

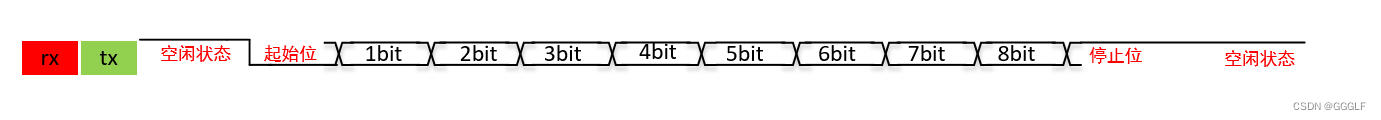

4. 序列 数据 的 传输 和 接收 是 基于 帧 结构,也就是说,从一个帧到另一个帧发送和接收数据。每个帧除了中间,还包含8位有效数据,每个帧的开头也必须有一个起点,并且固定到0;每个帧的末端也必须有一个停止,且固定为 1,基本框架结构(不计校正)为10位。在没有发送或接收数据的情况下,rx和tx处于闲置状态,此时Rx和Tx线保持高电压水平,如果传输数据帧,首先将有一个起点,还有8位数据位,然后有一个小站点,然后Rx和Tx继续进入闲置状态,然后等待下一个数据传输.如图30-7所示,这是基本的RS232帧结构。

这是十位数据,但第一位和十位分别是0和1,而中间的八位是任意的,所以你只需要传输中间的八位

第五速率:在信息传输渠道中,带有数据信息调用代码的信号单元(因为序列端口在1位列传输,所以它的代码元素代表一个二进制数),通过信号传输的每秒编码器的数量称为编码器的传输速率。简称波特率,普通符号“鲍德”的意思是:它的单位是“每秒Bps”。普通港口频率为4800、9600、115200等,我们选择9600比特率编译并模拟序列端口.

比特率: 通信通道每秒传输的信息量称为比特率.简称比特率,它的单位是“每秒bps”。比特率可以从比特率计算出来,这个公式是: 比特率 = 比特率 * 一个单个调制状态的二进制比特率。如果你使用9600位数,它的串行端口比特率为: 9600Bps * 1bit= 9600bps。

7. 通过 计算 的 序列 端口 传输 或 接收 1 位元 数据 的 时间 是 一 字节,也就是说,1/9600秒,如果系统时钟使用50MHz(周期20ns),计算的数目是cnt = (1s * 10^9)ns / 9600bit)ns / 20ns ≈ 5208系统时钟周期。也就是说,每位数据之间的间隔在50 MHz的时钟频率下测量5208次

8、当高级机器通过串口发送8位数据时,它在发送8位有效数据之前自动发送8位有效数据的初始位数,并在发送8位有效数据后自动发送一个停止位数类似地,一个序列助理必须在接收由顶层机器发送的数据之前检测到一个比特时间的开始点,然后在接收8位数据后,接收一个比特时间的停止点。

程序设计

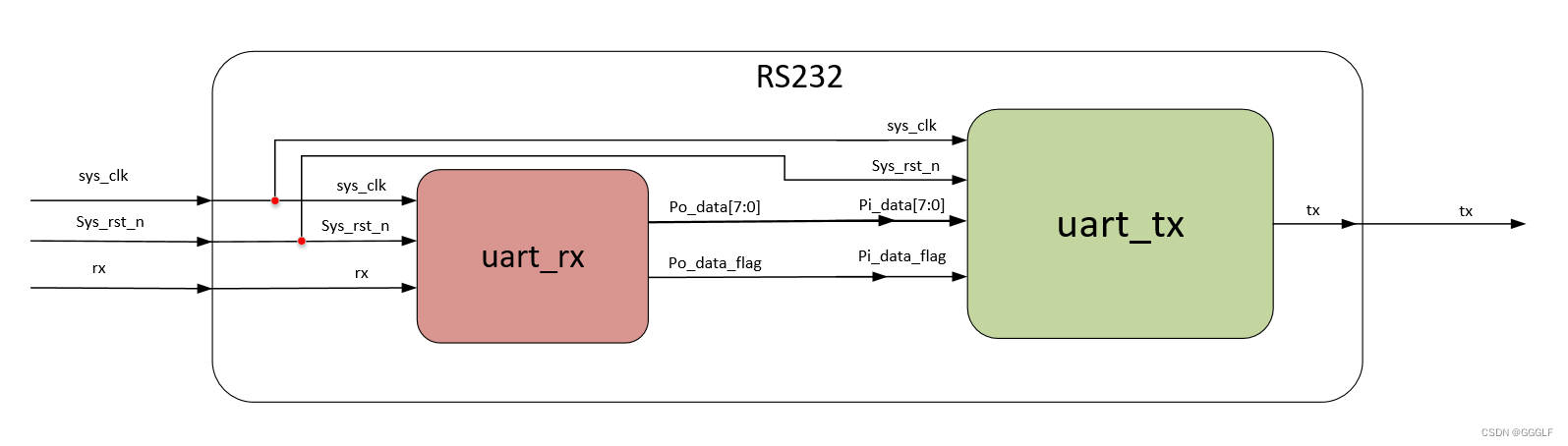

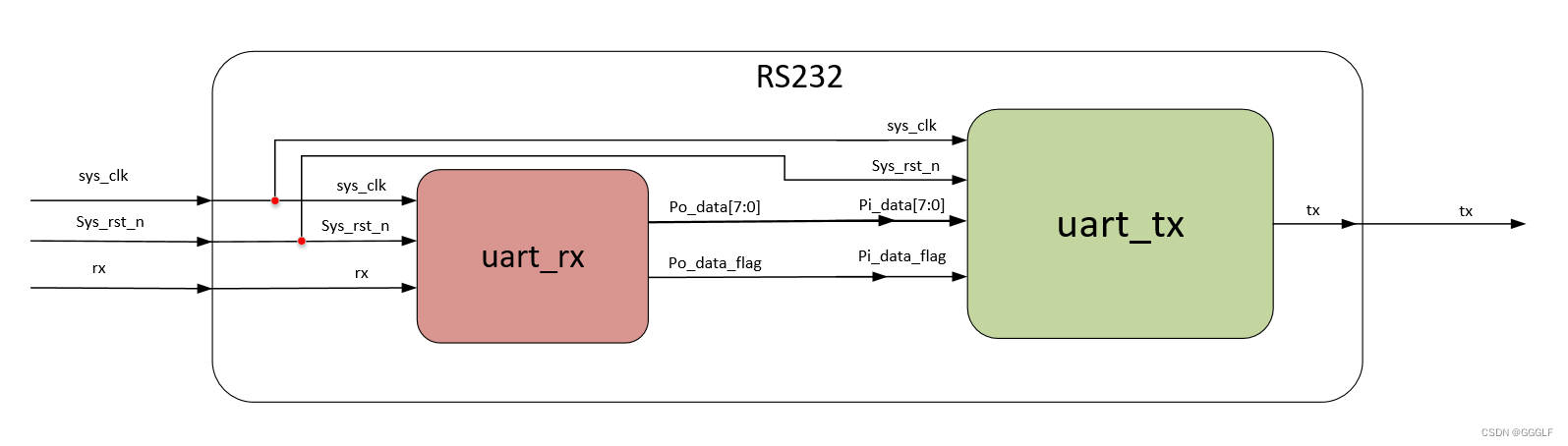

上层模块图如下:

如你可以看到,上面的面板包含两个模块,分别是接收模块和发送模块。

2、接收模块

接收器模块用于将PC输入的串行数据转换为平行数据。

每个帧有10位数据,开始和结束分别为0和1位,接收模块只接收中8位数据,将中8位串行数据转换成平行数据,然后输入8位平行数据到发送模块。

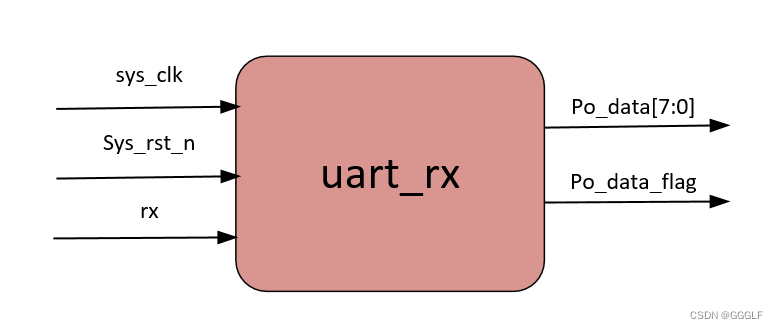

接收模块的图则如下:

接收模块波形图如下:

根据波形图描述代码如下:

接收模块仿真代码如下:

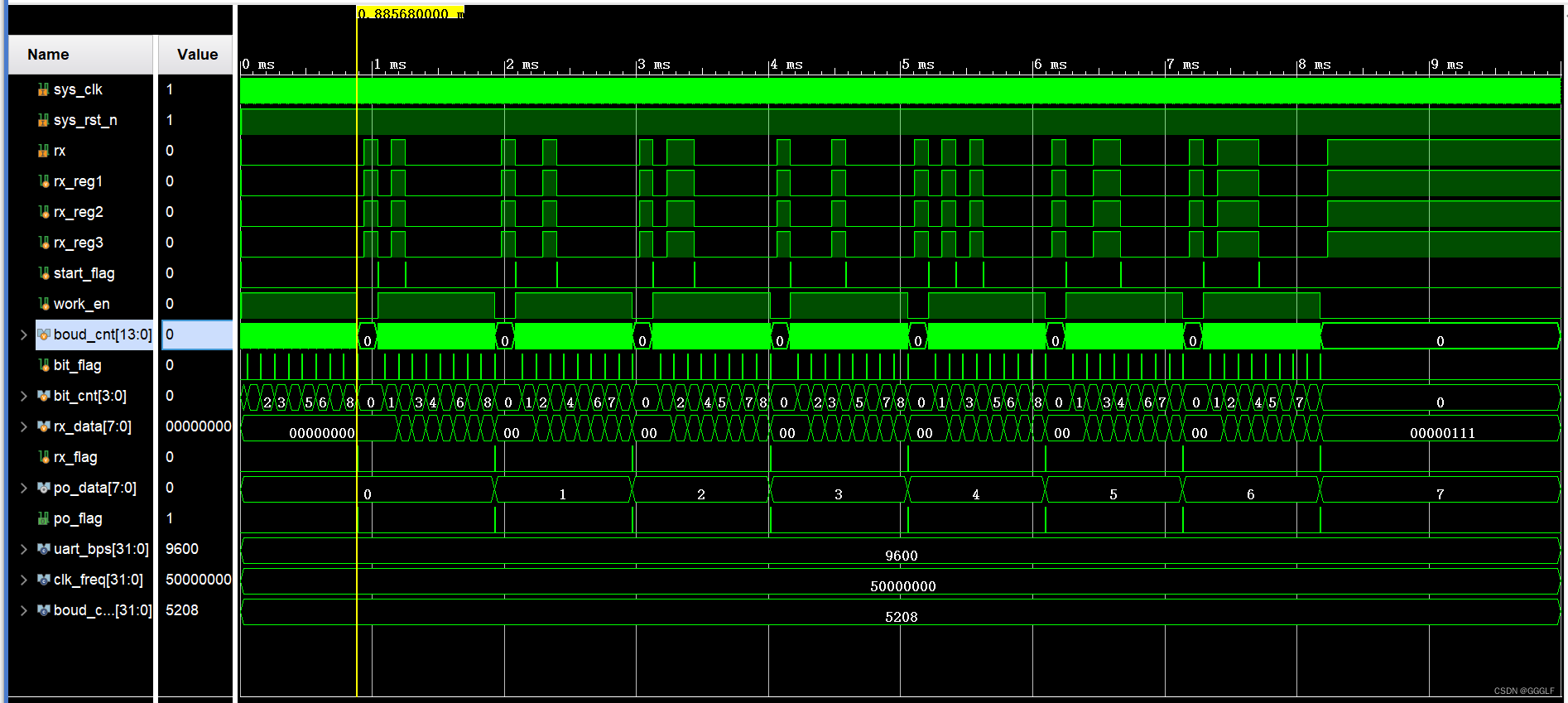

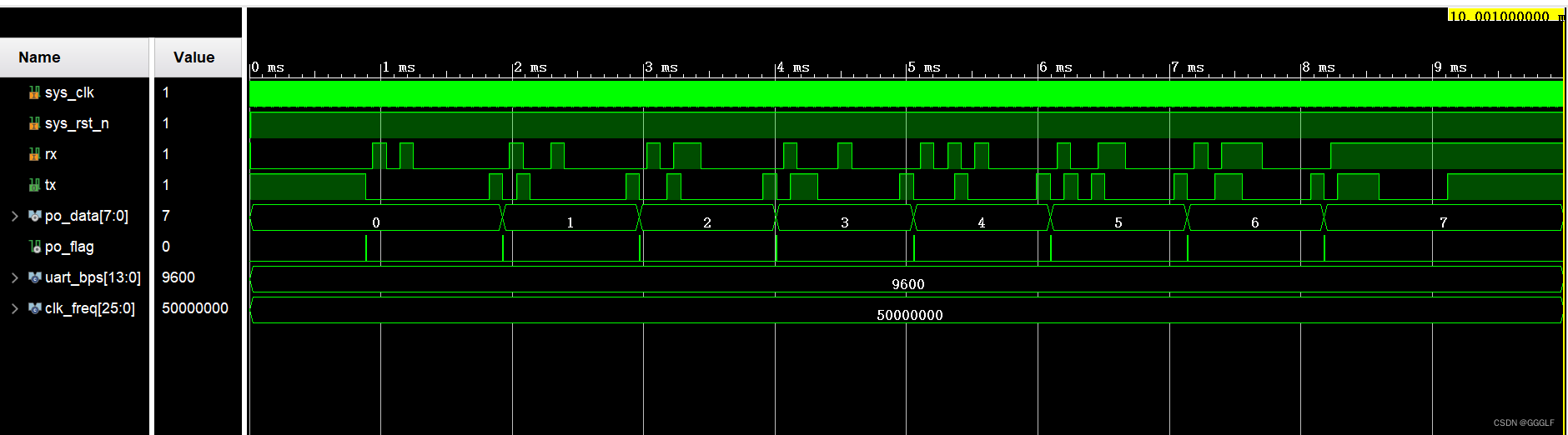

维瓦多模拟波形

整体波形如下

3、发送模块

发送模块的功能是从接收模块接收八位平行数据,然后将八位平行数据转换为一位串行数据,并将其逐一发送出去。

一个帧有10位元,第一个和最后的位元分别是0和1,从接收模块的数据的8位元位于中间。

模块设计

我们将调用串行接收器模块uart_tx,基于功能概况,我们对整体设计要求的全面了解,设计的关键是如何将串行平行数据转换成串行数据,并将其发送出去,这意味着,平行数据被发送到PC按顺序。FPGA发送的串行数据也没有时间表,所以你必须同意电脑使用相同的频率,把片子逐片发送,我们选择使用9600bps频率进行序列端口后路测试

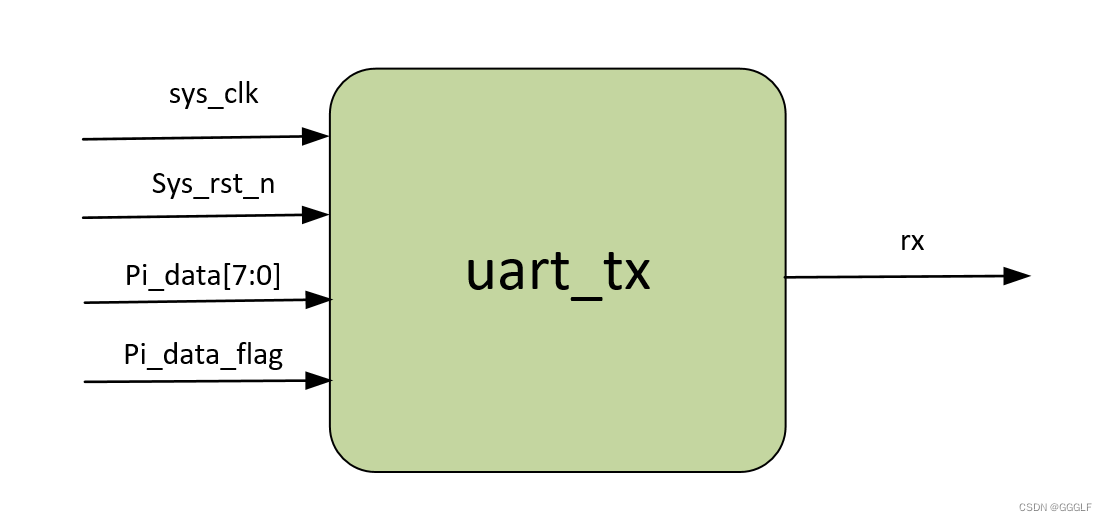

该模块的Visaio图如下:

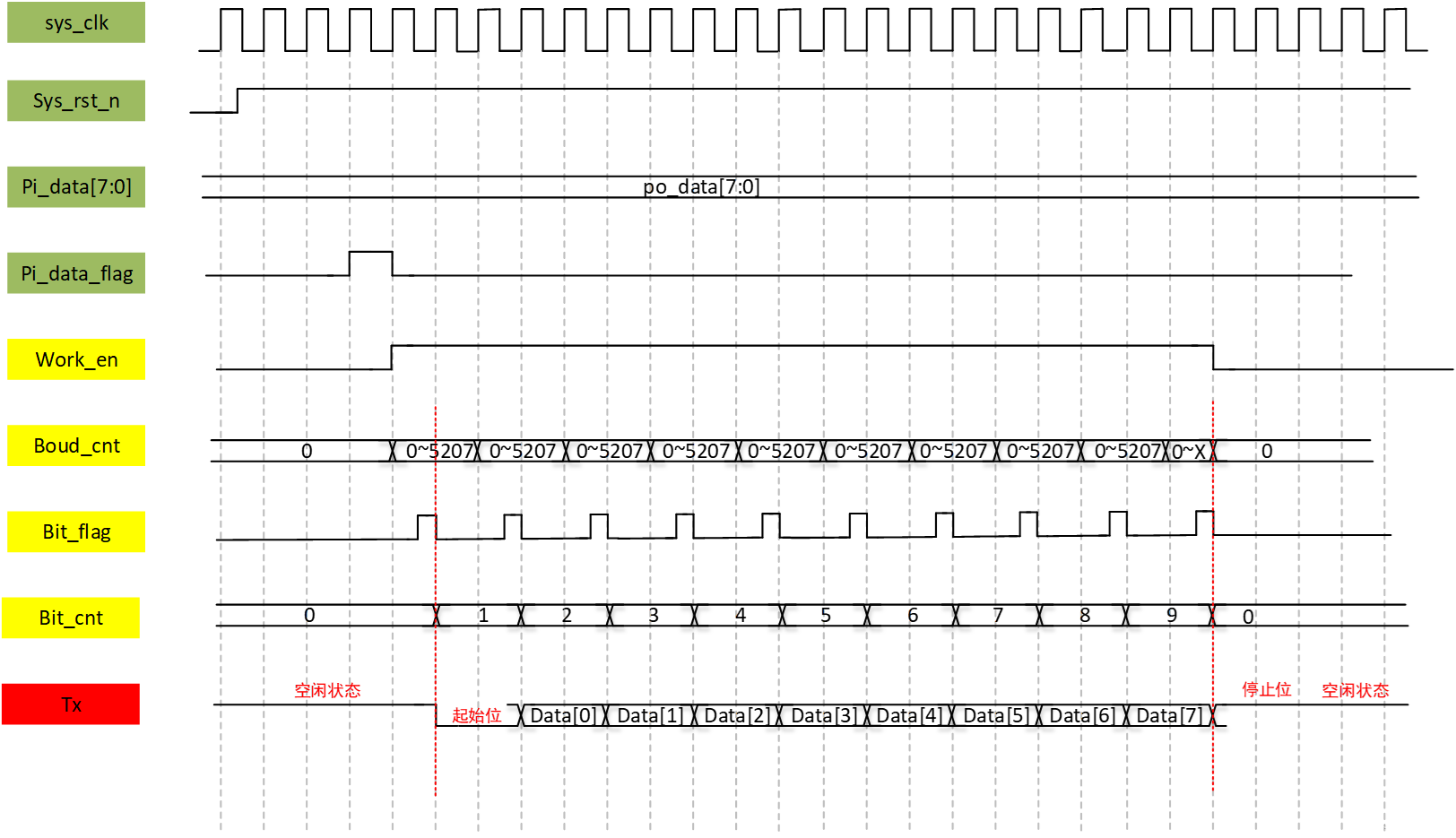

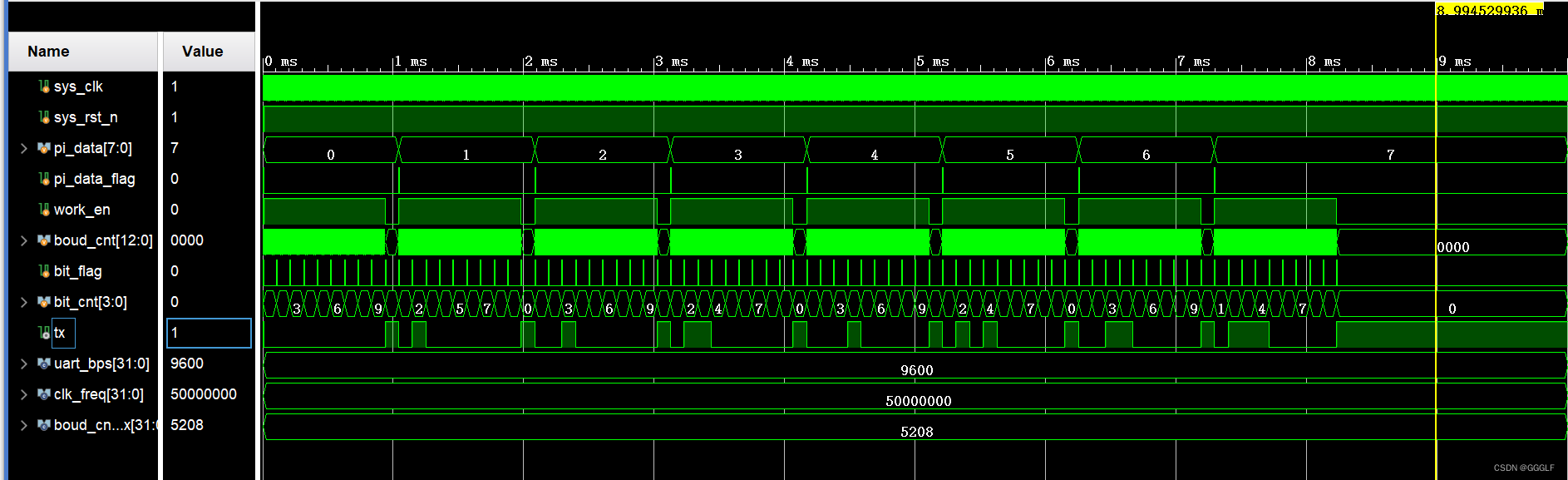

传输模块的波形如下:

ps: 注意,当第一个 bit_flag=1开始发送开始 bit 0,当第一个 bit_flag=9开始发送停止 bit 1时,同样的10位数据被发送,而剩余的Tx时间则处于闲置状态。

根据波形图,可以写下以下代码:

发送模块的仿真代码如下:

Vivado模拟波形如下:

顶层模块

顶层模块代码如下:

仿真测试代码如下:

维瓦多模拟波形如下:

本文由 在线网速测试 整理编辑,转载请注明出处。