PCI Express解析——系列文章【1】:基本概述PCI、PCI-X与PCIe的最大区别

- 1 PCIe概述

- 1 .1 基本简介

- 1.2 PCI, PCI-X和 PCIe

- 1.3 PCIe开发版本

- 1.4 PCIe数据链通道

最后更新:2022-07-17 06:00:24 手机定位技术交流文章

PCI Express分析-系列条目(1):PCI、PCI-X和PCIe之间最大的差异的基本概要

Author: Nirvana Of Phoenixl

Proverbs for you:There is no doubt that good things will always come, and when it comes late, it can be a surprise.

1 PCIe概述

1 .1 基本简介

PCI-Express(peripheral component interconnect express)是一种高速串行计算机扩展总线标准,它原来的名称为“3GIO”,是由英特尔在2001年提出的,旨在替代旧的PCI,PCI-X和AGP总线标准。

PCI-Express是第三代高性能的I/O总线,用于连接计算机和通信平台等外部设备。第一代包括ISA、EISA、VESA和微通道(Micro Channel)总线,第二代巴士包括PCI、AGP和PCI-X。PCIe是用于连接所有外接I/O设备,如移动设备、桌面计算机、工作站、服务器、嵌入式计算和通信平台的总线。

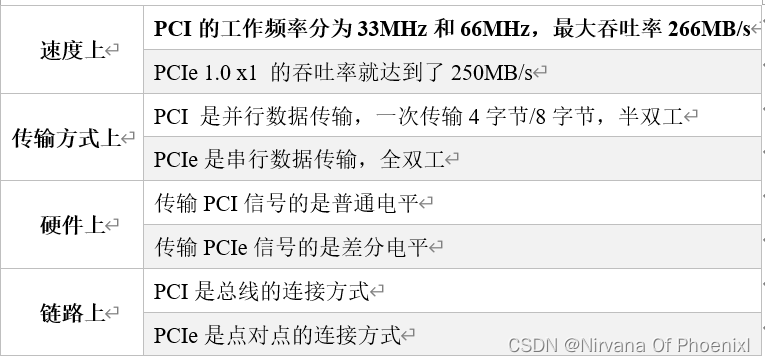

1.2 PCI, PCI-X和 PCIe

PCIe作为PCI和PCI-X的发展版本,其基本向后兼容,继承了第二代总线体系结构的有用特点,并有所突破。例如PCIe采用了与PCI与PCI-X相同的使用和读写通信模型。PCIe支持常见的事物,如存储器读写、IO读写、配置读写等事物。

在PCIe进化过程中,PCIe最明显的变化是系统结构的变化:

(1) PCI、PCI-X:公共汽车结构是一个多端平行互联的公共汽车。其中,多个设备共享一个总线,在单一的PCI总线上可以连接多个PCI设备,这些PCI设备通过一系列信号线连接到PCI总线,这些信号包括地址/数据信号、控制信号、仲裁信号、中断信号等。通过公共汽车循环实现;

(2) PCIe:能后实现两台设备之间的通信的串行、点对点类型的互连,多个PCIe设备使用交换器(Switch)实现互连;采用基于交换器的技术来互连大量设备,在串行互连上进行通信是利用基于数据包的通信协议来实现的。

PCIe和PCIe之间的差异在下面的表中显示

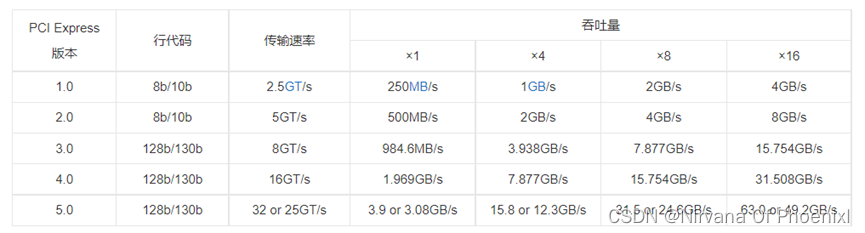

1.3 PCIe开发版本

PCIe版本经历了四个主要版本的更新,每个版本都有一个小版本,如1.1、2.1、3.1,小版本基本上没有特别的变化,所有基于大版本的优化。

(1)PCIe 1.0

2003年,PCI-SIG引入 PCIe 1.0a,每个频道的数据速率是250MB/s,传输速率是每秒2.5Gigatransfer(GT/s)。传输率是指每秒传输的数量,而不是每秒位数,由于传输的数量不包括额外的空间供额外的吞吐量; PCIe 1.x使用8b/10b编码方案,这导致使用原来的通道带宽的20% (= 2/10 ) 。

(2)PCIe 2.0

PCI-SIG于2007年1月15日发布PCI Express Base 2标准。PCIe2.0标准为 PCIe1.0至5GT/s的传输速率已翻一番,每个频道的容量从250MB/s增加到500MB/s。因此,32-通道PCIe连接器(×32)可以支持最大16GB/s的总吞吐量。PCIe 2.0主板插槽和 PCIe v1。PCIe 2.0卡也常被使用PCI Express 1.1是可用的带宽下降兼容PCI 1.x主板。总体来说,对于v2.0设计的卡或主板将与另一个v1.1或v1.0a用于使用。

(3)PCIe 3.0

PCI Express 3.0基本规范版本3.0在多个延迟之后于2010年11月提供。 2007年8月,PCI-SIG宣布 PCI Express 3.0将有一个每秒8Gbit的位数(GT/s),它将与现有的PCI Express兼容。PCI Express 3.0将编码方案从以前的8b/10b编码升级为128b/130b,PCI Express的宽带扩展从0的2.20%减少到大约1.54%(=2/130)。这是通过一种叫做干扰的技术实现的,该技术将应用已知的二进制多项式在反馈拓扑中的数据流。

(4)PCIe 4.0

2011年11月29日,PCI-SIG宣布PCI Express 4.0提供16Gb/s比特率,使得PCI Express 3.0提供了带宽的翻倍,同时保持与软件支持和二手机械接口的后向兼容。

表1 PCIe版本迭代

1.4 PCIe数据链通道

将两台设备连接在一起的一个PCI Express互联称为一条链路。一条链路在每个方向上可以有x1、x2、x4、x8、x12、x16、x32个信号对,这些信号可以称为通道,设计者根据需求确实实现通道。

| 链路 | 特点 | ||||||

|---|---|---|---|---|---|---|---|

| PCIe链路宽度 | x1 | x2 | x4 | x8 | x12 | x16 | x32 |

| 总带宽(GB/s) | 0.5 | 1 | 2 | 4 | 6 | 8 | 16 |

下一条: PCI Express 分析 - 系列条目 (2): PCIe 的原理分析 - PCI Express 线的基本原理

本文由 在线网速测试 整理编辑,转载请注明出处。