使用 ZYNFPGA 序列通信进行实验

最后更新:2021-11-07 15:58:17 手机定位技术交流文章

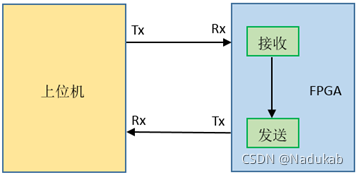

实验任务

数据从顶端机器通过序列端口传送到开发面板,数据通过序列端口返回顶端机器。

TXRX是FPGA收到的一份系列来文,送交平行数据。

协议层:

数据位为 8 位,停止位为 1 位,无校验位

波特率为 115200bps

目标是将上图中的数据转换成平行数据并生成信号。

序列摄入的流程图 :

uart_rxd收到了来自 uart_done 的八个平行信号。

当收到 uart_done 信号时,该信号将保持高度的港口利率周期,表明以下平行信号是合法数据。

Start_flag 是序列接收过程的起始信号, 当 uart_rxd 坠落时, 序列接收过程会提供高电高度系统时钟周期 。

Rx-flag 表示接收程序结束 。

1/115200(时速)是每次数据传输所需的时间。

clk_cn 计时系统时钟周期,最多一个端口速率周期,然后是零,然后又开始计数。一个波特时钟率一次计数,表示数据传输。

rx_ cnt +1 点出行速率周期的小时数后各自的位置。字符串和转换或标签,视值而定,在平行数据的相应位置上方插入相应的比特。

串口接收代码:

系列传输模块图表:

uart_en在停车时效率低下,必须随着攀爬而被发现。

代码:

顶层:

本文由 在线网速测试 整理编辑,转载请注明出处。