TDC 7200时间间隔测量由FPGA(二)控制。

- 端口定义

- 状态定义

- 地址命令定义

- SPI时钟确定

- 字节数确定

- 最先进的最先进的 最先进的 最先进的 最先进的 最先进的 最先进的 最先进的 最先进的 最先进的 最先进的 最先进的 最先进的 最先进的 最先进的 最先进的 最先进的 最先进的 最先进的 最先进的 最先进的 最先进的 最先进的 最先进的 最先进的 最先进的 最先进的 最先进的 最先进的 最先进的 最先进的 最先进的 最先进的 最先进的 最先进的 最先进的 最先进的 最先进的 最先进的

- 数据发送

- 数据接收与传出

- 脉冲模拟

在将应用程序上传到董事会之前,先通过模型模拟运行。启动后,我们创建了START和停止脉冲信号,核查TDC FPGA控制的时间序列,并构建脉冲程序和测试台如下:

最后更新:2021-12-06 06:08:30 手机定位技术交流文章

继续上文内容:

https://blog.csdn.net/qq_46284844/article/details/121716619?spm=1001.2014.3001.5501

这是关于TDC 7200的一些基本资料,本条讨论如何利用FPGA来操作TDC 7200。

整体思路

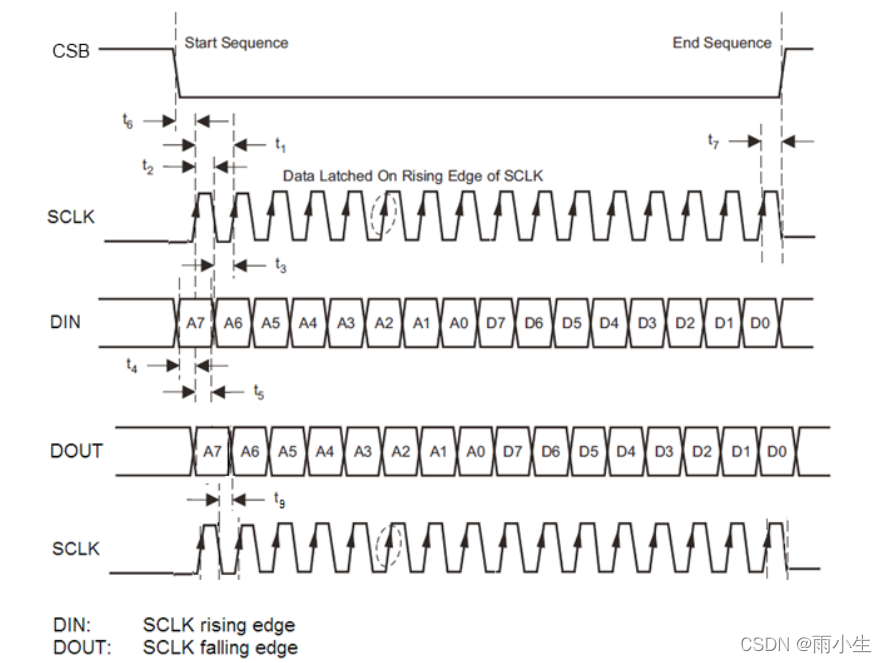

TDC 7200用于SPI通信,因此我们首先认识到建立SPI通信协议的要求,然后根据数据手册的保存地址和相关设置发送和接收数据。 最后,我们像我们通常一样使用状态机器来控制FPGA的时间序列。

程序介绍

如前所述,港口的定义如下:

(1) 计时和重新定位信号;

(2) 当TDC暂停用于答复调查的进口港口时,说明完成情况;

(3) 提供四个SPI站点和一个TDC 7200来调节管脚。

(4) 有两个与数据有关的港口,一个是数据港口,另一个是数据有效性港口。

状态定义包括:

(1)初始状态;

(二) 关闭电源信号,然后将其打开,然后关闭用于转移TDC的赋能信号1;

(三) 发出信号,如前一条所述,这需要一段时间稳定,然后5毫秒同时稳定;

(4) 随后进行了一系列初始化工作,根据SPI数据流特点和TDC 7200手册的描述,FPGA必须在每次将数据写给TDC之后背读有关数据长度的数据,以便能够阅读和写下一份,这样,每份指令都需要两个州,一读需要一个州;

(5) 初始化状态是等待TDC测量并推进到下个阶段的状态,即 tdc_间断港被推倒。

(6) 检查TDC状况;

(7) 等待重置状态。

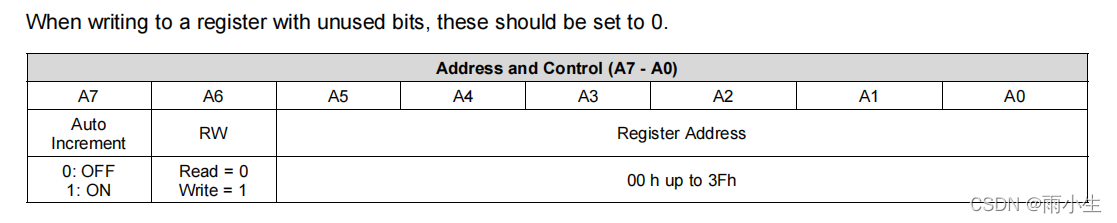

前11项指令与启动指令的状态相对应, 接下来3项指令是读取测量后数据的指示, 我们定义了整个 0 命令在读取时要传送, 原因是 SPI 的回传数据结构 。

命令是这样拼凑起来的

仍然可以追溯到这张图,数据从这个图中传送到数据中的预地址,直到TDC, 再到TDC。 所以我们都得遵循前面的地址和后面的数据。 一旦数据格式已经确定, 我们就可以根据数据手册中的注册地址来确定六位数的地址信息, 加上八位数地址的格式, 加上八位数的顶层自动增长和次高读的数据。

简而言之,我将12分钟的晶体钟数转换为50兆赫.5兆赫SPI钟,在TDC 7200文件显示的所有时间保持最高频率。

这里有很长一部分的文特字节 专用于代码

如前所述,最长期限是数据分配过程,因为TDC的登记号是8或24,因此我们很难将16个稍用一点,所以我们每8个稍用一点。 所以,50兆赫主钟、12.5兆赫SCK钟、50/125.5* 8=32个单位。 至于为什么所有32小时都作为时间计算周期使用,由于创建时间、保留时间、CS拉动时间等等,对提及Fire的SPI代码时间序列作出了规定,从而大大简化了时间序列的编制,节省了代码的长长段。

以下是各州的Cnt_byte年表以及计算关系表:

基于以上所述,我们正在开发 状态跳跃代码如下:

国家与DELY状态之间的跳跃开始阶段已经没有多少讨论了。 我们可以看到,如果我们在等待TDC阶段从TDC中测量到一个信号,我们就会跳到读TDC国家READING_TDC,根据前一条款,我们需要读三个发件人(TIME1, CALI1, CALI1, CALI2),因此有三个阅读时间序列,全部是24个地点,这样,在将地址寄过去之后,我们就可以读三个数据框架(与前两个数据表格不同,会有四个)

如上文的代码所示,我们可以收集我们需要根据当前周期传输的数据,然后根据高级别概念发送。

由于SCK沿数据下降,对警方的时间序列进行监管,当SCK_CNT在0: 00下降时,我们推迟一个时钟周期来阅读数据,即将数据通过比特移动,以便数据可以读出来,我们就可以在8或1之后获得数据并发送出来。

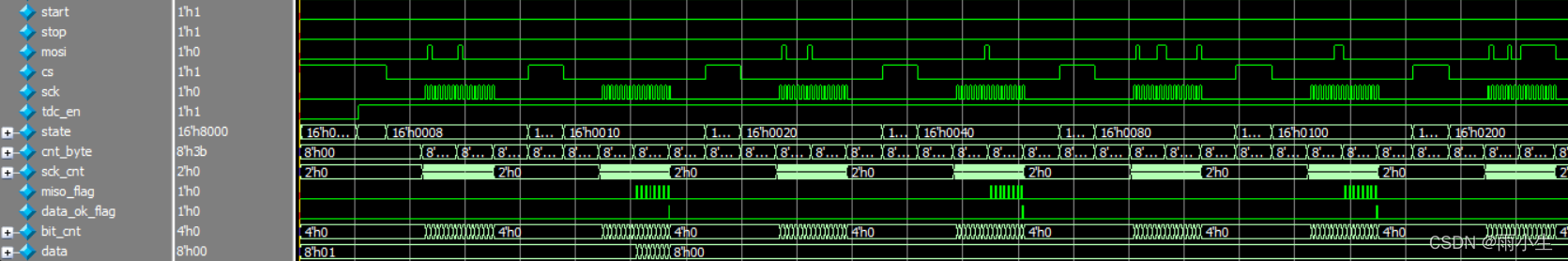

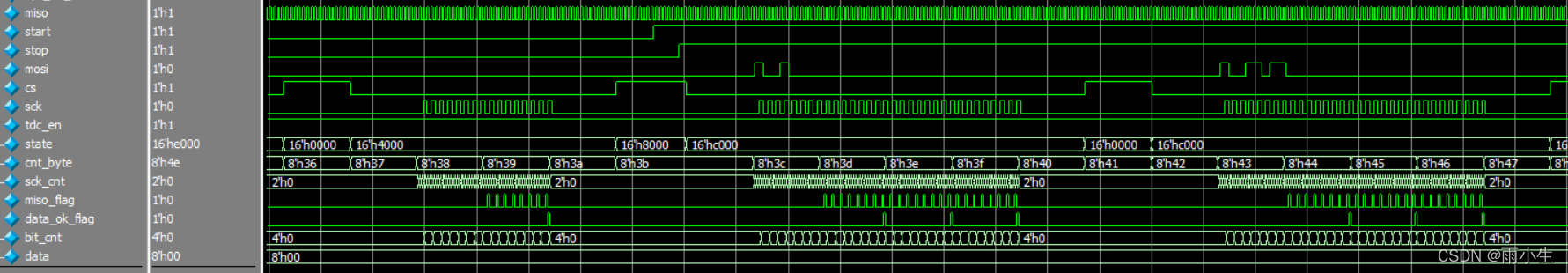

仿真现象

CS信号、SCK信号和MOSI在启动时能量信号被击落后都正常。

在START和STOP信号之后,我们模拟了一个INTURRUPT信号,接着是三次24位读数、模拟和板测试。

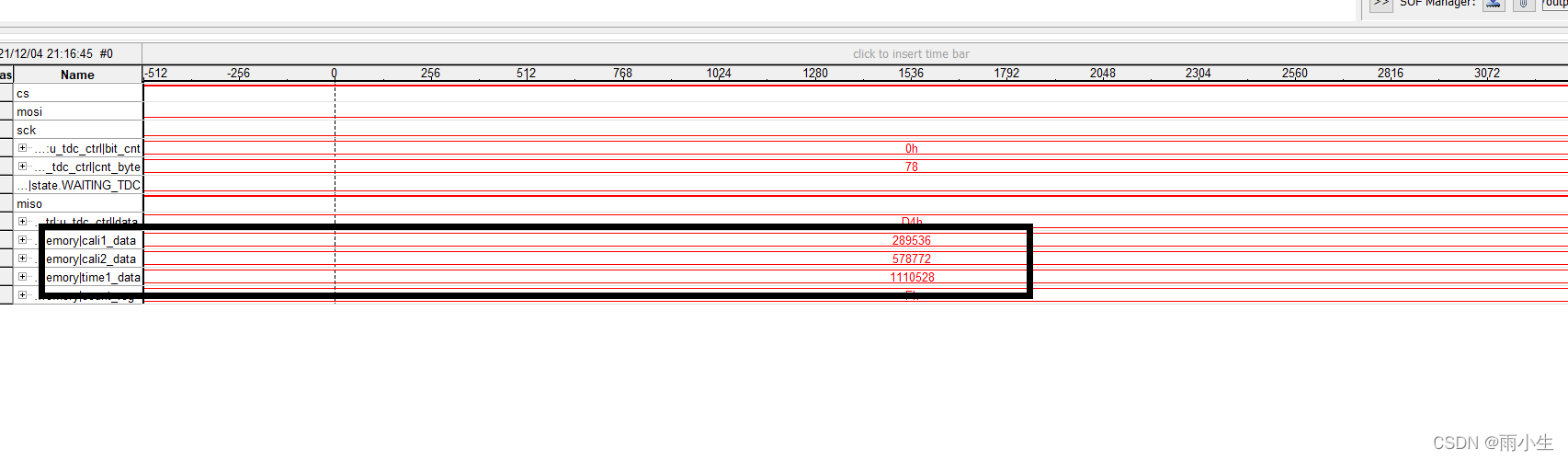

实际测试

由于屏幕显示的复杂性,结果在信号塔普中显示,暂时不写。然后,由于暂时没有时间间隔,FPGA本身创建了脉冲,作为脉冲测量。START和STOP间隔设定为240 ns(12个时钟周期)。

以上图表中读取的数据使用前一条所述方法计算:

calCount = (cali2_data - cali1_data) / (2 - 1);

normLSB = CLOCKperiod / calCount;

TOP = TIME * normLSB;

callot = 289,236,normLSB = (1/16M) / 289,236,TOOP = 110528 *normLSB = 0.23997.us = 239.97ns

错误: abs( 239. 97 - 240. / 240 = 0. 125 / 千)

替换时间间隔定为200毫秒,数据再次收集如下:

同样的计算方法:

calCount = (cali2_data - cali1_data) / (2 - 1);

normLSB = CLOCKperiod / calCount;

TOP = TIME * normLSB;

CalCount = 289,237,规范LSB = (1/16M) / 289,237,TOOP = 926720 *normLSB = 0.20025us = 200.25ns

abs (200) 25- 200 是一个错误。 (00) 除以 200 等于 1.25 / 00 。

误差分析

(1) 逻辑大门的长度可能推迟;

(2) TDC结晶的精确度受到限制。

(3) 没有因差分输入+Dubon传输钟脉冲造成的信号移动。

写在最后

项目代码包含在其中,它使用Altera的CYCLONONE4系列EP4CE22作为控制器,作为Quartus II 13. one建造环境。

com/s/1VQ-v_mxFFfIkhN9Qj9XTEBQ 我们特别报导全球之声在线.com/s/1VQ-v_mxFfIkhN9Qj9XTEBQ

提取码:dpwe

本文由 在线网速测试 整理编辑,转载请注明出处。