芯片常用协议种类详解,含多协议转换器_IClance999的博客 ...

- 引言

最后更新:2021-12-22 21:14:49 手机定位技术交流文章

题目: 芯片用于详细界定协议类型,并含有多协议转换器。

目录

1. 引言

1.1常用通信样式

一,FPGA芯片的UART是相同的。

一.3 FPGA用Averilog法实施UART

1.4 完成了基于方PGA的SPI协议

1至5个通过菲律宾竞争和消费者保护局的多种协议转换。

P an德

FPGA 以十年为重点的硬件工程师

FPGA&芯片的定制开发、技术交流+V好: xinpianxiehui

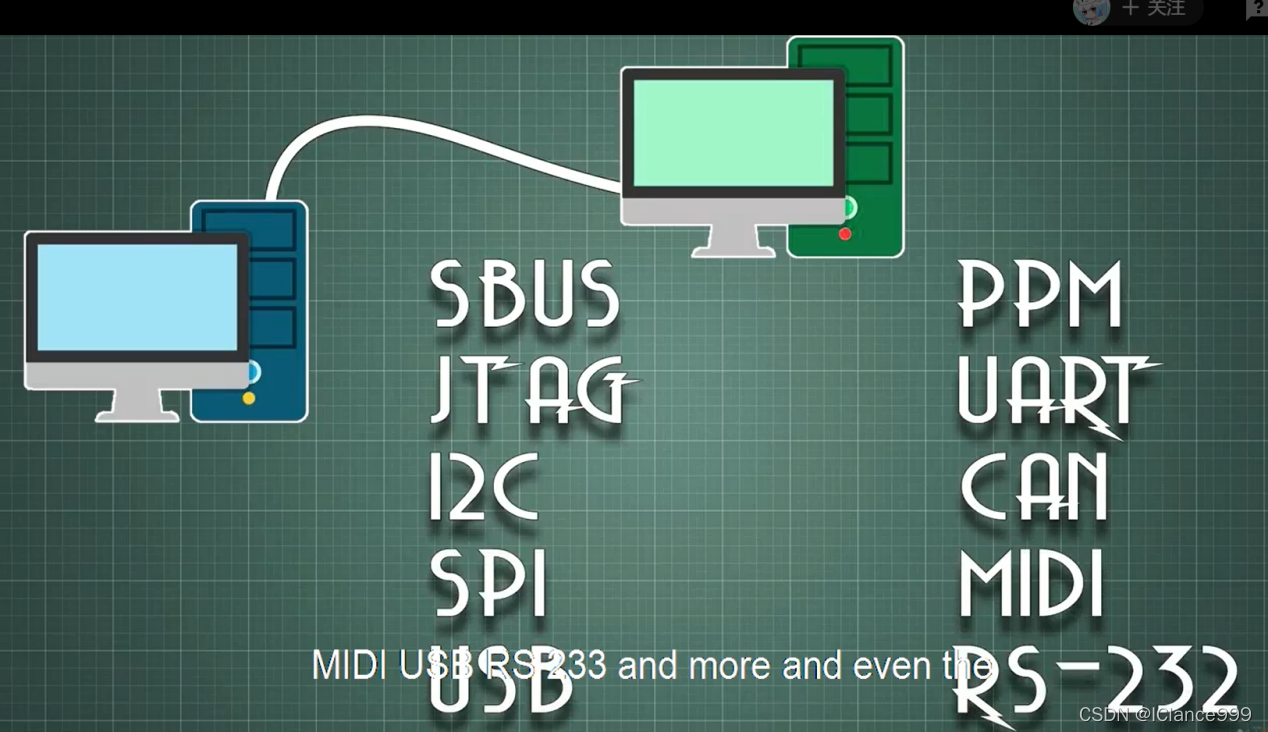

为什么你需要一个沟通协议,就像一个人的语言, 如果没有语言信息, 芯片就像一个哑巴, 你不知道发生了什么? 通讯的二进制信息主要包括时间 CL、 地址、 数据, 以及一个速率。

1.1常用通信样式

要么是一条直线 要么是一条平行线

要么是一条直线 要么是一条平行线

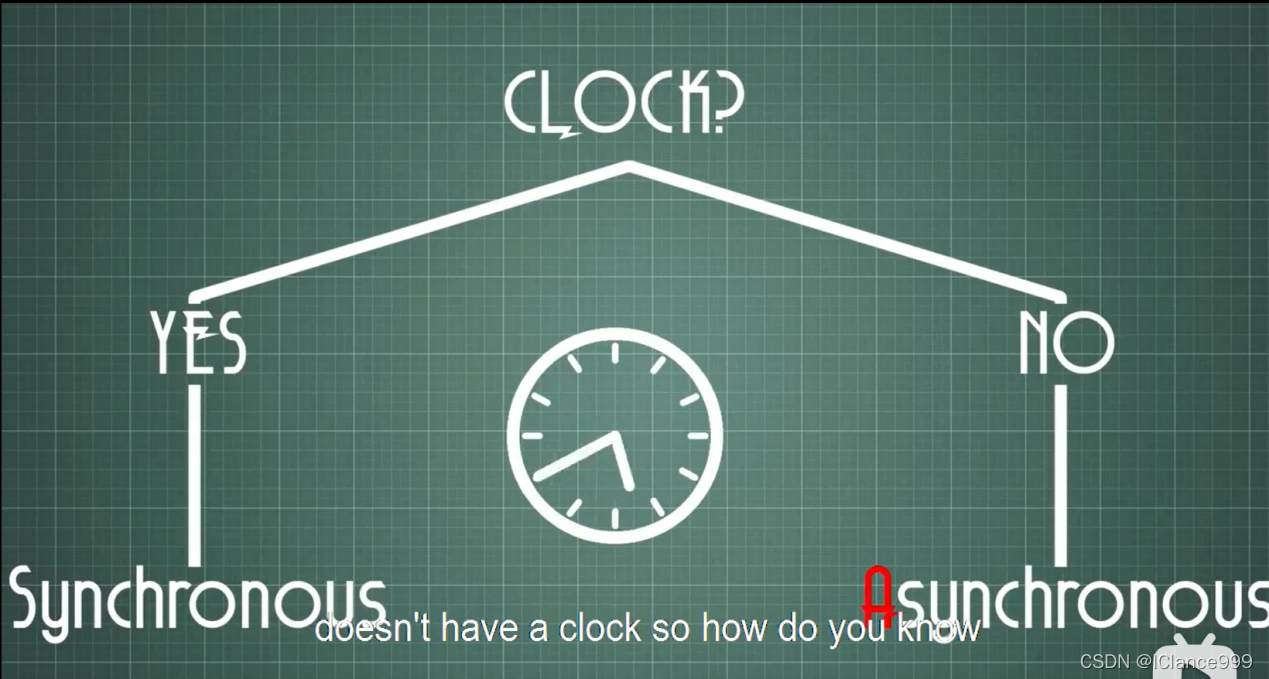

一个是计时器 另一个是计时器

一个是计时器 另一个是计时器

一. 传输率. 2. 数据长度. 3. 开始和结束

I2C one.one.1 可用

理论上最多可管理127个地址设备。

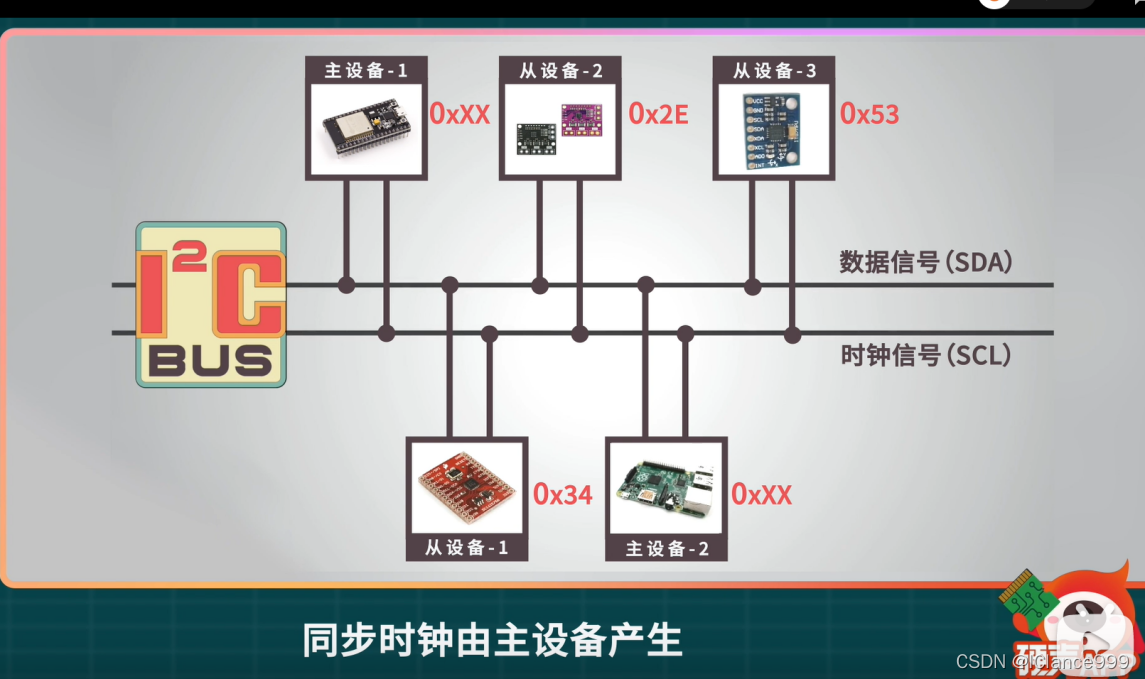

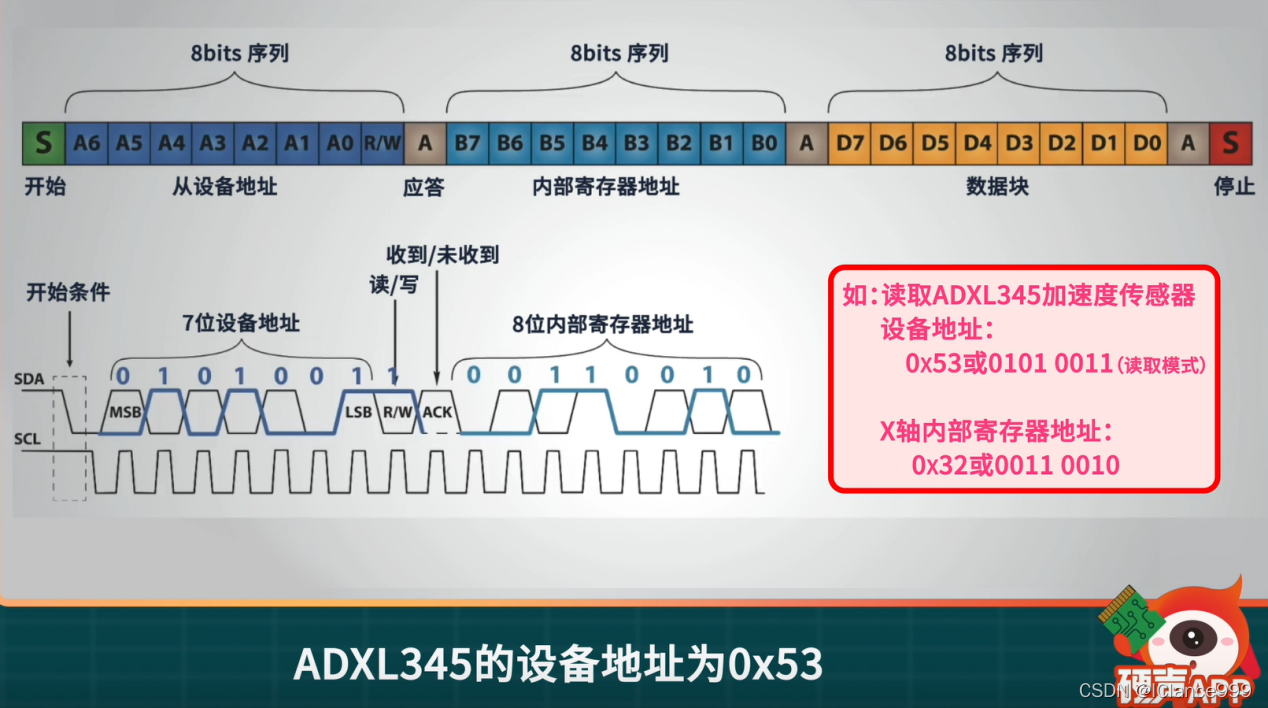

PHLIPS创建了I2C(集成电路)公交车,这是一条双线连线系列公交车。连锁公共汽车由数据线SDA和时钟线SCL组成。可发送和接收数据。它被用来将微控制器及其外围连接在一起。I2C巴士于1980年代首次出现。它最初是为视听设备设计的。目前有若干用途,最明显的是各种电气设备。I2C公交车的主要优点是其简单性和有效性。

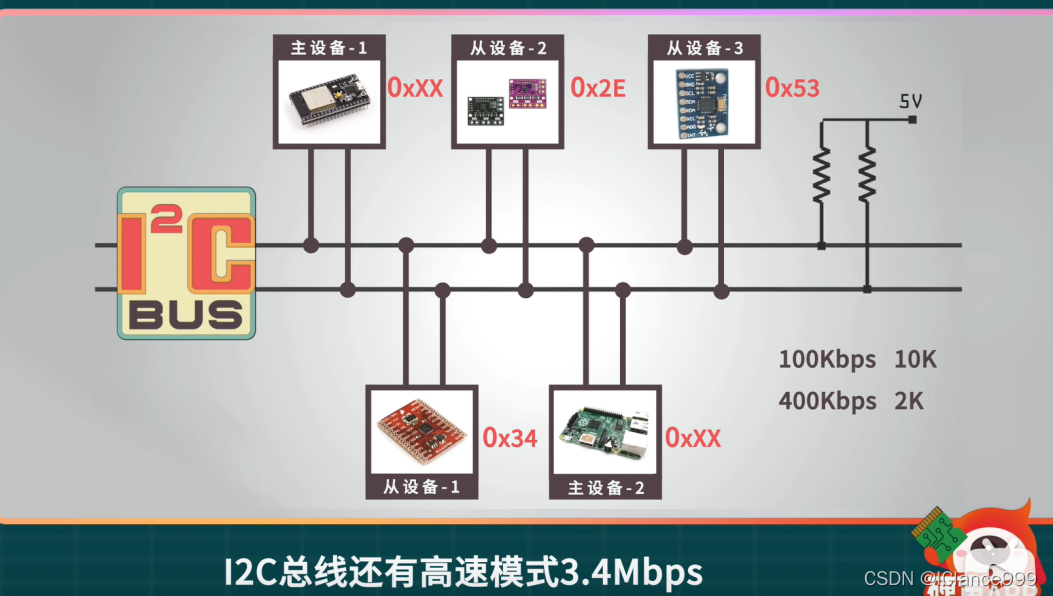

I2C大客车消耗的空间极小,因为接口就在部件上方,减少了电路板空间和芯片管脚的数量,降低了连通费用,总客车最长可达25英尺,最多可容纳40个部件10千位/秒。 。 (这种传输率因I2C总线的长度和相关部件的数量而异,理论最高为400千位/秒。 )

100Kbps 具有10K抵抗力 400Kbps 具有2K抵抗力

I2C 公共汽车的另一个特征是它能够实现多重混乱,这意味着任何能够发送和接收数据的装置都可能成为主车。 控制信号传输和时钟频率的主机。 当然,任何一个时刻都只能有一个主机。

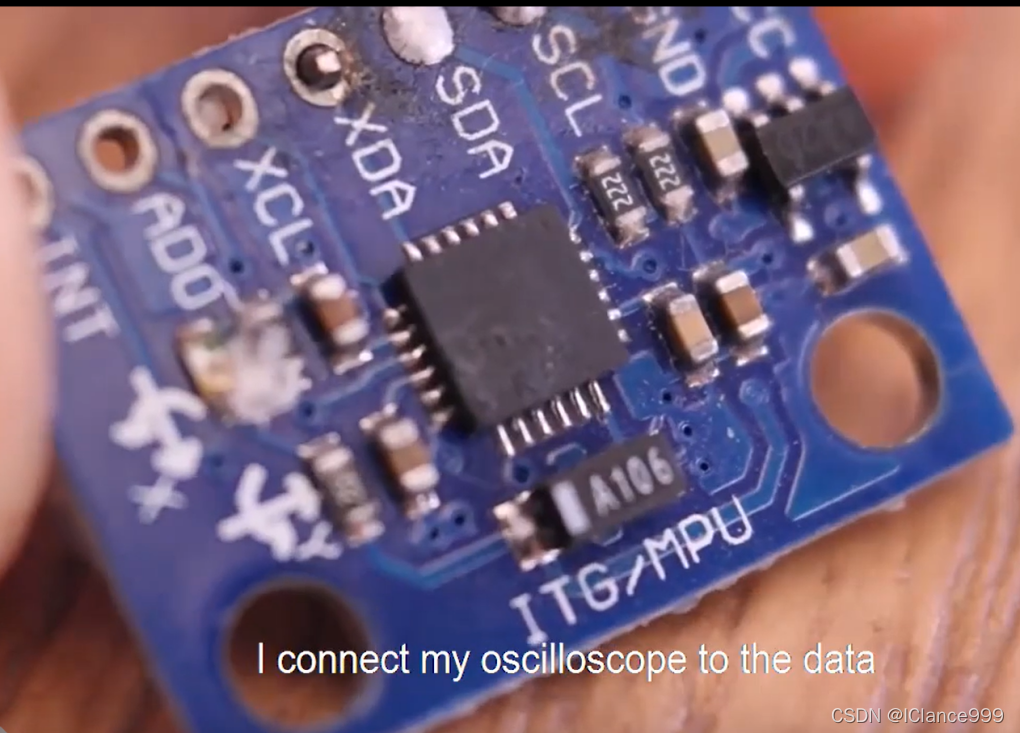

集成I2C的芯片

I2C总线是连锁公共汽车由数据线SDA和时钟线SCL组成。可发送和接收数据。CPU与索赔的IC、IC和IC之间的双向通信。最大传输速率为400千位/秒。这条公交线路连接所有受管制的电路。主控制设备随时生成时钟信号 。

I2C大客车载有传送数据的三个基本控制信号:启动信号、终端信号和回答信号。

当短链氯化石蜡高时,自失能装置会从高向低过渡。

当短链氯化石蜡高时,自失能系统从低向高转变,数据流结束。

反应信号:接收数据的仪器在收到数据后,向传输显示收到数据的数据的装置发送低级别信号。该信号可能来自主控制装置或移动装置,但总是由接收数据的仪器发送。

需要启动信号,最终信号和响应信号可能被拒绝。

I2C总线操作

I2C协议申请/双向通信所有者数据由设备发送到总线 。则定义为发送器,接收器是接收数据的装置。主设备和工具都可以在接收和传输模式中发挥作用。主要装置(通常是微控制器)必须控制公共汽车。主要装置产生一个序列钟(SCL),控制公共汽车的传输方向。也创建起始和停止标准 。SCL在SDA线上的数据状态只是低功率

SDA状态的改变是为了表明在SSCL高度的平段期间的开始和停止情况。

一. 1.1.2 标准SPI

SDI(数据输入)、SDO(数据输出)、SCK(时钟)和CS(选择)是缩略语。

(1) SDO - 主设备数据输出,从设备数据输入(通常缩写为MOSI)

(2) SDI - 主设备数据输入和输出(又称MISO)

(3) SLK - 主设备时钟信号。

(4) CS - 主装置(又称SS)发出的电源信号

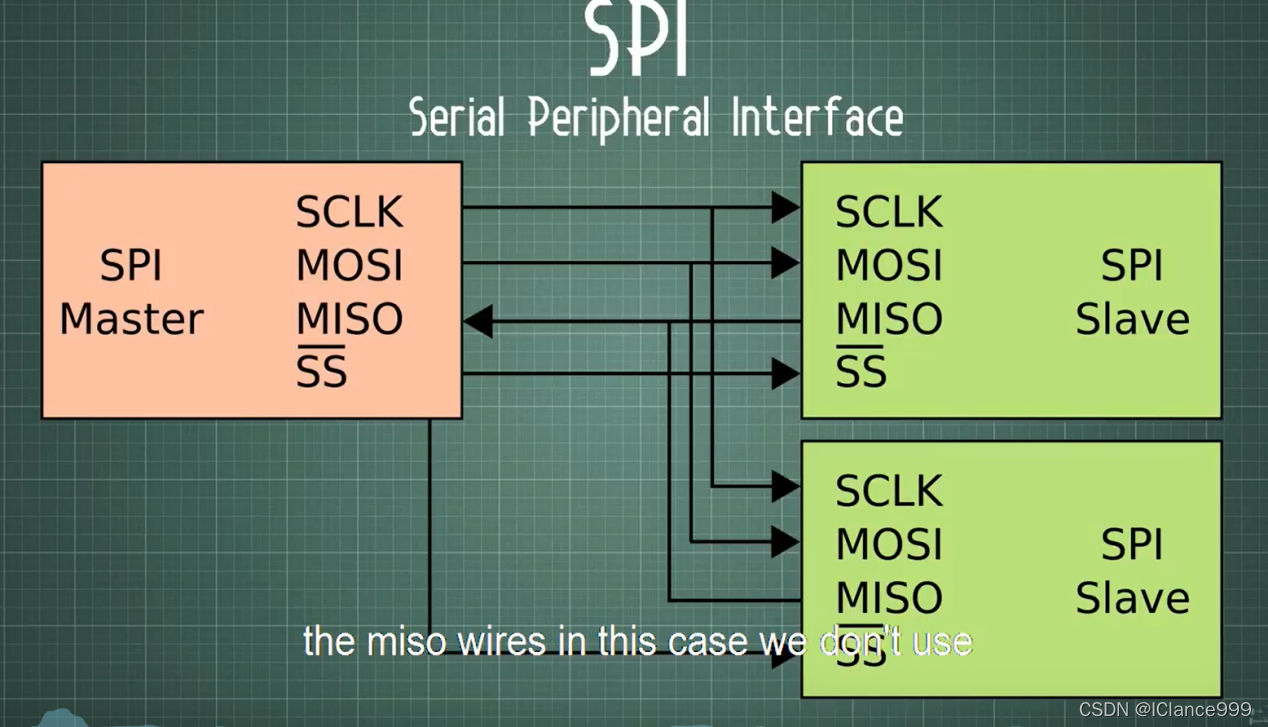

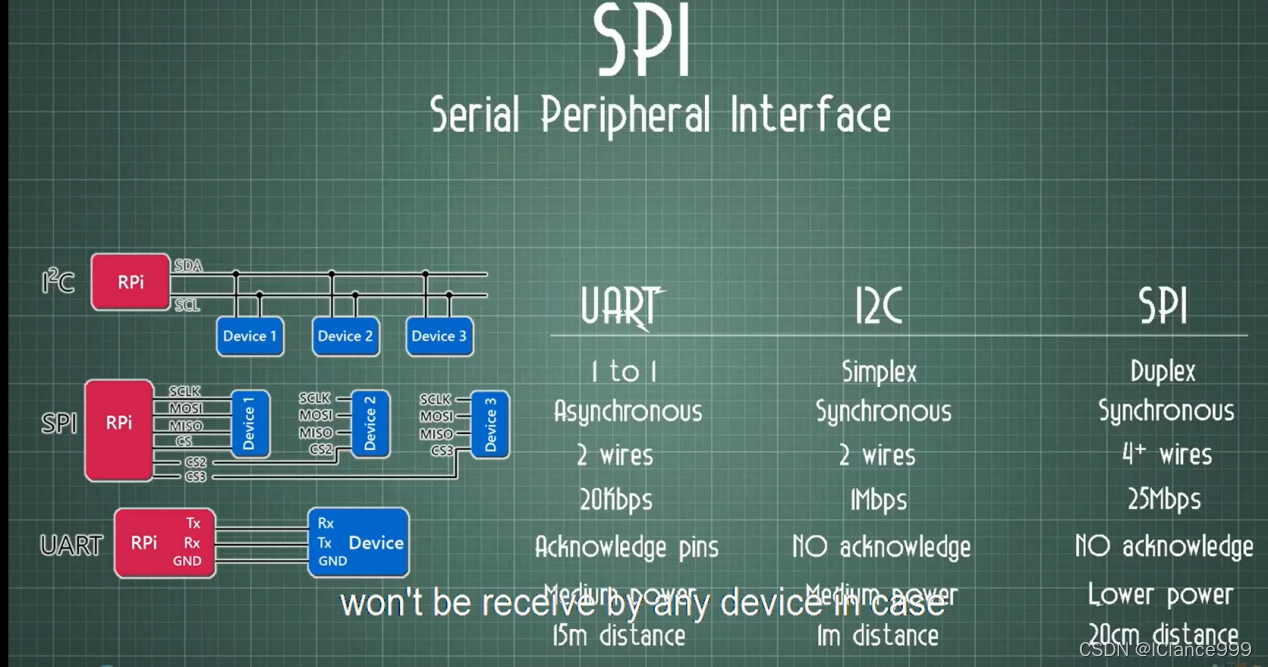

SPI是英文串行周边界面的缩略语。在中文中,它指链条边缘之间的一个界面。Motoola发明了SPI,这是一个同步的通信链。这是一个同步的三线公交车。因其硬件功能很强,与SPI有关的软件比较简单。让处理器更长时间地处理它。他事务。

SPI对SPI的描述如下:高速同步序列交叉点3-4线界面、独立、同步。

SPI,这是英文连环边界面的缩略语顾名思义,它是一个连环外围装置接口。SPI接口主要在EPROMs中使用。FLASH,实时时钟,AD转换器,此外,数字信号处理器与数字信号解码器之间有一个鸿沟。SPI是一个高速接口。全双工,同步的通信总线,芯片管脚上只有四根电线节约了芯片的管脚,它还节省了多氯联苯布局的空间。提供方便。目前,越来越多的芯片正在使用这一通信议定书。

SPI公共汽车系统是一个外部同步链界面。它使MCU能够与各种外围装置相接,相继进行信息交流。FLASHRAM、网络控制器、液晶显示驱动器、A/D转换器、多边协调单位和其他外部设置SPI公共汽车系统可以与各工厂制造的许多标准外围直接通信。通常,接口由四行组成:

SPI的传播原则是直截了当的。它以主从方式工作,这种风格通常包括一件主要设备和一件或多件设备。需要至少4根线,实际上,其中三个可以(单向传输)。它也由所有基于SPI的装置共同使用。它们SDI(数据输入)、SDO(数据输出)、SCK(时钟)和CS(选择)是缩略语。

(1) SDO - 主设备数据输出,从设备数据输入(通常缩写为MOSI)

(2) SDI - 主设备数据输入和输出(又称MISO)

(3) SLK - 主设备时钟信号。

(4) CS - 主装置(又称SS)发出的电源信号)

CS 用于规范芯片是否被选中, 也就是说, 芯片的动作只有在单个选中的信号是预设启用信号( 高或低) 的情况下才会有效。 这使得许多 SPI 设备能够连接在同一总线上 。

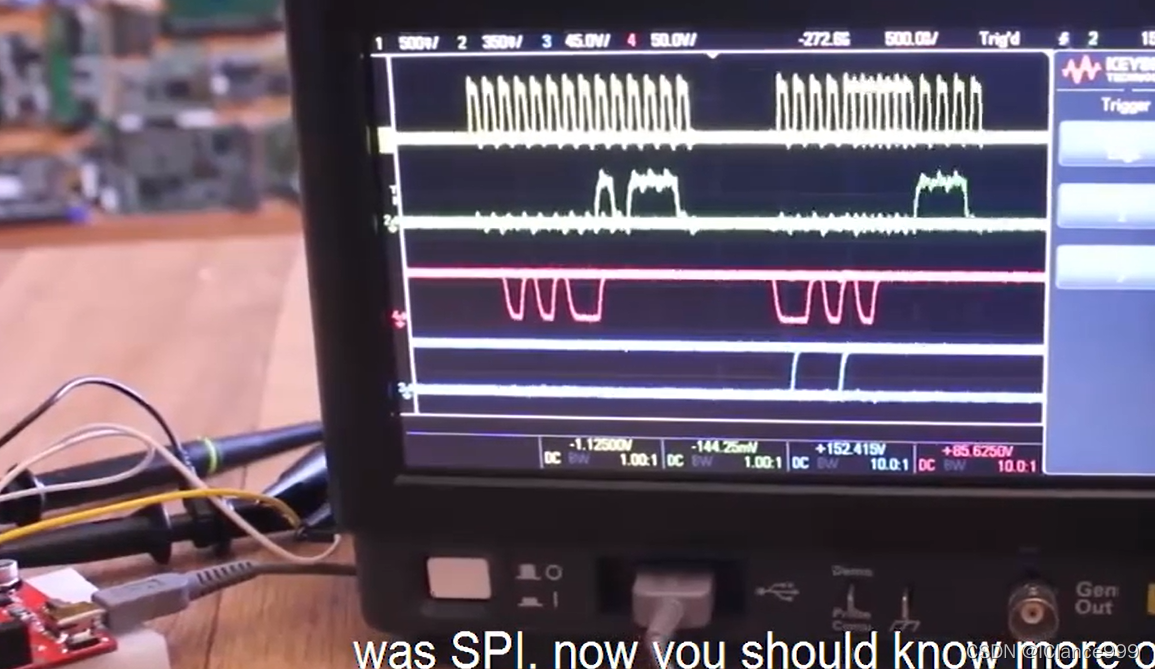

以下三条线路负责通信。交换数据用于通信。SPI是指一套通信协议。也就是说,数据是由单个个人传输的。这就是为什么创建SCK时钟的原因。SCK生成时钟脉冲。SDI,根据脉冲,SDO完成数据传输。数据是通过 SDO 线的输出。当时钟上升或下降时,数据就会改变。在近乎低迷的低迷中 一起读或往上读完成一位数据传输,这里提出了同样的原则。这样,时钟信号至少需要八班(一次上下)。你现在可以完成八位数的转换了

要注意的是,只有主要设备能控制SSCK信号线。工具无法控制信号线同样,当使用基于 SPI 的设备时,至少,有一个总控制装置。这种传播的特点:这种传播方式有一个好处。这与定期的系列来文不同。典型的序列传输连续发送至少连续发送八个数据包。此外,SPI还允许单个个人传输数据。甚至允许暂停,因为主控制装置负责SCK时钟当没有时钟跳变时,设备数据没有收集或转让。也就是说,主要设备可以通过控制SCK时钟来控制通信。由于SPI的数据输入和输出线是独立的,它也是一个数据交换协议。使数据输入和输出同时进行。若干SPI装置以不同方式实现。这主要是由于数据变化和获取数据所需时间不同。在时钟信号上或下收集信号的定义不同。请特别参见该装置的文件。

就业绩而言,由于线条和平行职能更多,因此SPI的转让比I2C短、更快。SPI接口有缺陷:没有说明流动控制,也没有确认数据接收的响应机制。

就业绩而言,由于线条和平行职能更多,因此SPI的转让比I2C短、更快。SPI接口有缺陷:没有说明流动控制,也没有确认数据接收的响应机制。

SPI

SPI

SPI接口不需要在点对点通信中进行定位搜索操作,而且对全时双重工作通信来说既简单又高效。 在许多设备系统,每个设备需要单独的推进器信号的硬件都比I2C系统复杂一些。

最后,SPI接口有缺陷:没有说明流动控制,也没有确认数据接收的响应机制。。

一,一,三是标准UART。

(Universal Asynchronous Receiver/Transmitter)

一根线来通信

通用异步收发器

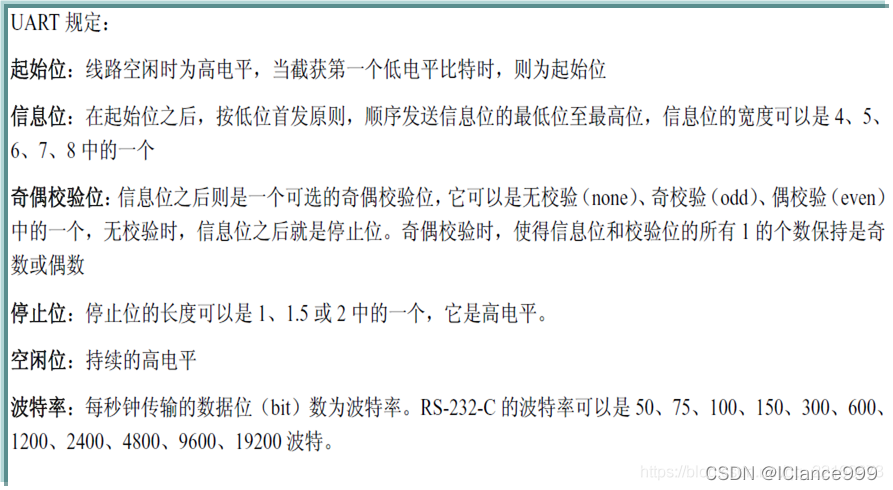

UART是一种用于操作计算机和序列设备的半导体,它提供RS-232C数据终端接口,使计算机能够通过RS-232C接口与调制解调器或其他序列设备连接。

UART系统主要由数据总线接口、控制逻辑、港口费率发电机以及传输和接收部件组成。- 功能包括微处理器接口。数据接收缓冲(rbr),接收迁移登记(rr)、框架生成、奇迹检查、浏览和浏览,发送缓冲(tbr),发送迁移登记(tbr),发送迁移登记(tsr)、框架生成、娃娃核查和旋转,数据接收缓冲(rbr),接收迁移登记(rr)、框架生成、奇迹检查、浏览和浏览

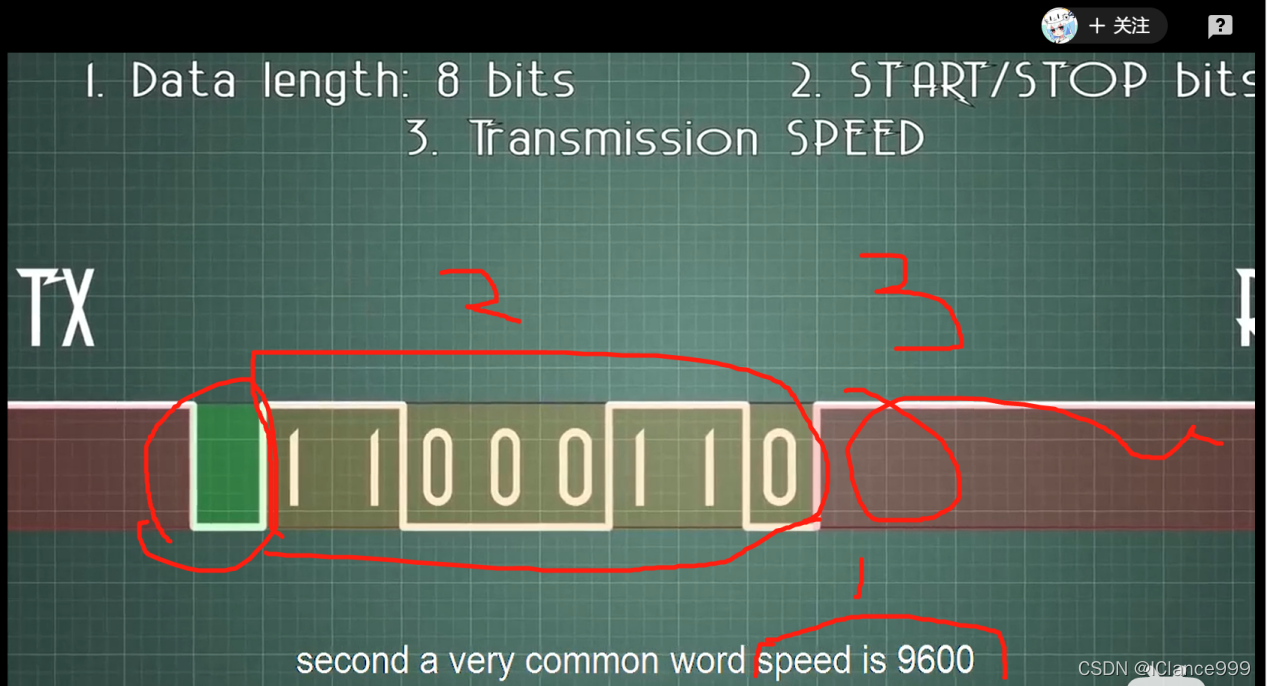

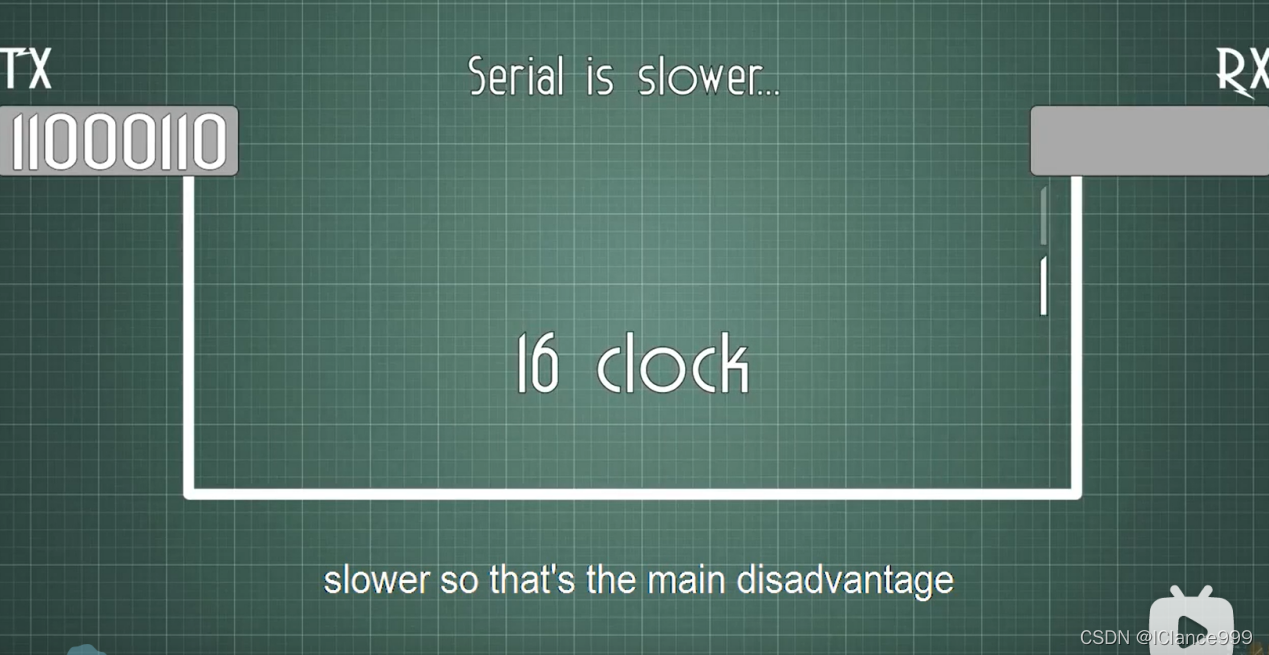

UART协议是各装置之间低速数据传输的标准协议,不同于同时发送时钟,因为没有必要同时发送时钟。

在四台STM32上进行序列剖析

1.2 FPGA 联合议定书

1、概述

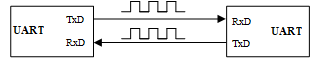

UART代表世界非同步收发机/发报机。通常称作UART。UART港包括四个连接器(VCC、GND、RX、TX)、TTL级、低端0(0V)和一个地针。高公寓被定义为1/3.3V或以上)。

UART是用于非同步通信的典型序列数据总线,以两种方式进行通信,并允许全时双重工作传输和接收,UART可被描述为由许多计算机通信设备使用的一台单一机器的基本配置。

RX是数据接受界面的缩略语。

为了有效运行,TX连接到两个设备之间的RX,RX连接到TX。最经常的情况是,我们计算机上的USB是最受欢迎的UART接口。

UART在正常的TTL/CMOS逻辑水平(0.55v、0.3v、2.5v或0)上运行。高电平表示1,低电平表示0。为了增强数据的阻力和传送时间长度,通常,TTL/CMOD逻辑水平被转换为RS-232逻辑水平。3~12v表示0,- 3 -12v 表示 1。

数据线 TxD 和 RxD 将数据以位数向最小单位发送 。该框架由若干相互关联和不可分割的组成部分组成。它包括开办、数据、报到(如有必要)和中途站。发送数据之前,UART必须商定数据传输的速度(即每次需要多少时间)。波特速率是上一个数字)、数据传输格式(即有多少数据位置、是否使用检查、是否使用奇点检查或玩具检查、以及有多少停位位)。

数据传输流程如下:

(1) 自由:常规数据线不受限制(1个状态)。

(2) 传送起始位置:在发送数据时,UART将改变TxD数据行的状态(改为0),并保留一位计时器。

接收器然后确定起始点,等待1.5秒钟的时间,开始对交付的数据逐条测出数据线的状况。

(3) 发送地点:一个UART可在一个框架中持有5、6、7或8位数据,在这样一个框架中,发射机将数据线的状态逐条改变并发送,从最低位开始。

(4) 奇数检查点:如果使用检查功能,UART在提供数据后也派出一个检查站,有两种核查方式:奇数检查,甚至检查——检查点的数据位数相当于奇数或甚至值。

(5) 停止位数: 最终, 传输停止和数据线返回到闲置状态( 状态 1 ) 。 有三种停止位数: 1 位、 1 位、 5 位和 2 位 。

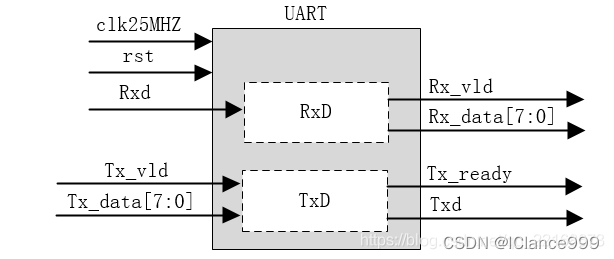

2. FPGA基于FPGA的UART 序列设计做法

2.1需求分析

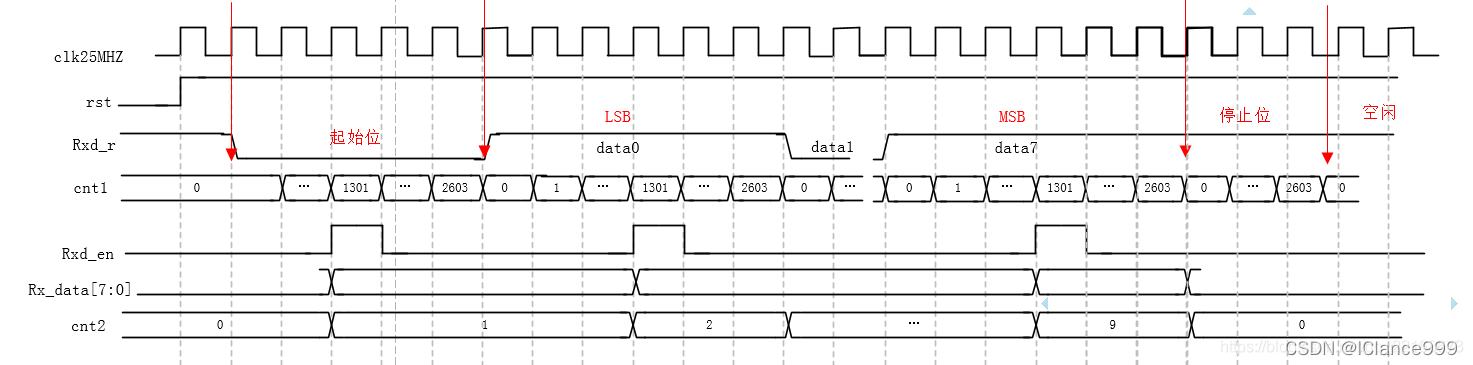

Sys_clkB25MHZ, 波特速率=9 600, 开始=1, 信息=8, 无奇特检查站, 停止=1

波特速率=9 600,一个信息时段为1/9600秒,这意味着在25兆赫时需要2604钟周期。

Rxd_r的数据取样始于单位数数为1301时,使用计数范围为[0:2603]的计数器。

Rxd_r 是一个 rxd 信号, 是 rxd 跨时钟字段的数据, 由 clk25 MHz 三发操作生成的 rxd 信号 。

架构如下:

tx-ready: 高水平显示 UART 准备接受 tx- data [7:0] 数据 。

UART接收数据的时间窗口在下面的图像中描述。

UART接收了RxD数据。

UART数据传输的时间序列,与以上所示相同,无

FPGA&芯片的定制开发、技术交流+V好: xinpianxiehui

专注FPGA15年

一.3 利用Averilog 以FPGA为基础的UART

AI 计算和访问 -- -- FPGA论坛 -- -- FPGA/CPLD学习论坛 -- -- 21世纪电子技术发展论坛

1.4 FPGA SPI协定的实现

AI 计算和访问 -- -- FPGA论坛 -- -- FPGA/CPLD学习论坛 -- -- 21世纪电子技术发展论坛

1至5个通过菲律宾竞争和消费者保护局的多种协议转换。

AI 计算和访问 -- -- FPGA论坛 -- -- FPGA/CPLD学习论坛 -- -- 21世纪电子技术发展论坛

本文由 在线网速测试 整理编辑,转载请注明出处。