verilog I2C_eeprom 手册分析及代码编写思路

- 型号(EEPROM):24LC04B

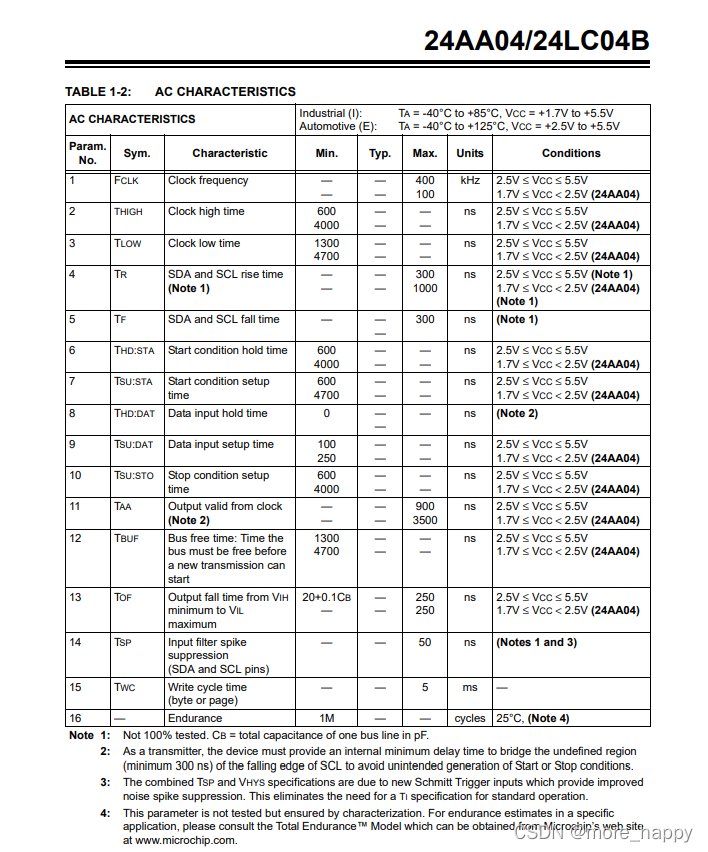

- 时钟频率:100-400KHZ

- 两线串行接口,兼容I2C协议

- 电可擦除,断电数据不会丢失

- 两个block,每个block :256*8bit.总共内存4kbit

- TBUF:Bus free time: Time the bus must be free before a new transmission can start,两次传输之间需要等待1300~4700ns;

- 其它的保持时间和建立时间在时钟频率设定在100~400Khz时都是正确的

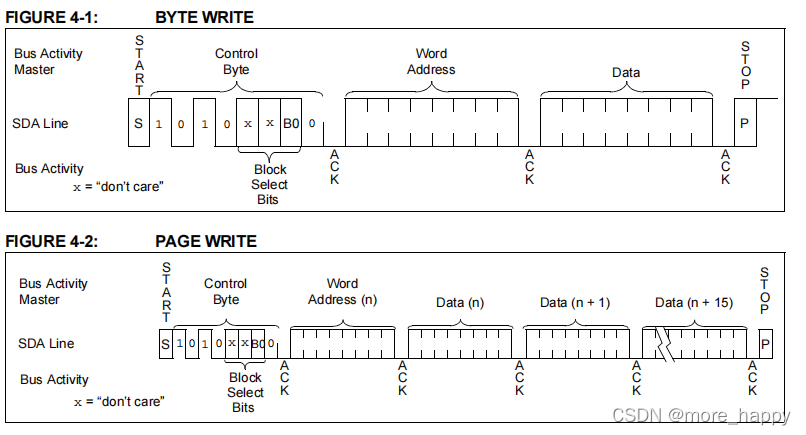

- 发送起始位:SCLK高电平时,SDA拉低

- 写入控制字节:设备地址(1010)+任意两位(xx)+block选择(0/1)+读写控制(1/0)

- 等待从机应答:从机控制SDA拉低

- 写入字节地址:word address(eeprom 中block中的地址)

- 写入数据:SCLK低电平时,主机控制SDA写入数据

- 发送停止位:stop

- 发送起始位:SCLK高电平时,SDA拉低

- 写入控制字节:设备地址(1010)+任意两位(xx)+block选择(0/1)+读写控制(1/0)

- 等待从机应答:从机控制SDA拉低

- 写入字节地址:word address(eeprom 中block中的地址)

- 写入数据:SCLK低电平时,主机控制SDA写入数据

- .

- .

- .

- 写入第16个数据

- 发送停止位:stop

- 每一bit都需要一个sclk周期完成

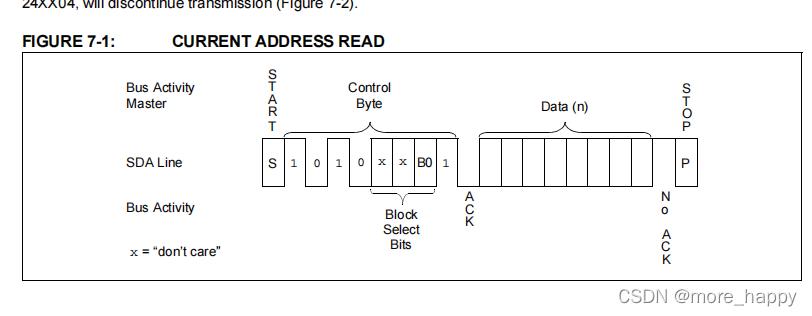

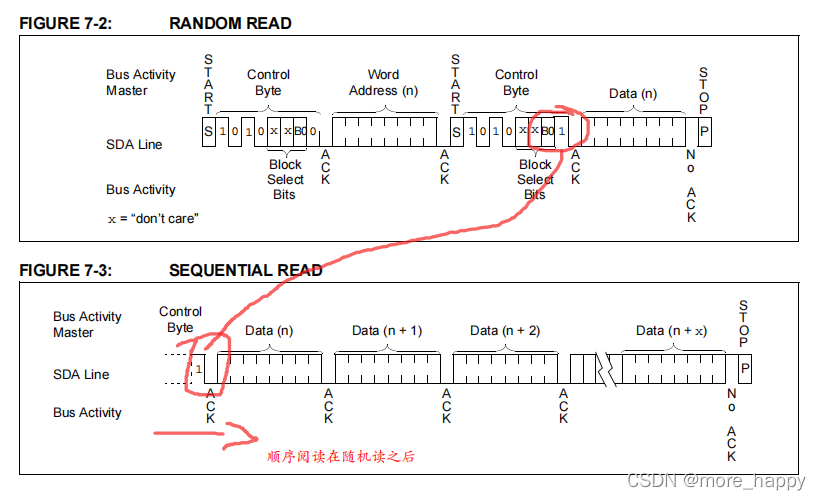

- 发送起始位:SCLK高电平时,SDA拉低

- 写入控制字节:设备地址(1010)+任意两位(xx)+block选择(0/1)+写控制(0)

- 等待从机应答:从机控制SDA拉低

- 写入字节地址:word address(eeprom 中block中的地址)

- 发送起始位:SCLK高电平时,SDA拉低

- 写入控制字节:设备地址(1010)+任意两位(xx)+block选择(0/1)+读控制(1)

- 读取数据:SCLK高电平时,读取数据SDA

- .

- .

- .

- 读取最后一个数据

- 发送停止位:stop

- 每一bit都需要一个sclk周期完成

最后更新:2022-01-24 07:21:11 手机定位技术交流文章

verilog I2C_eeprom 手册分析及代码编写思路

.基本属性_EEPROM_24LC04B/24AA04

一.AC特性表

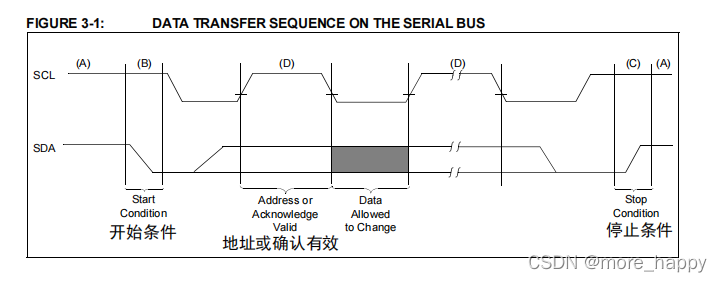

二.I2C协议数据读写时序图,起始停止图

1.数据总线和时钟线在空闲时都必须拉高

2.开始条件:时钟总线高电平时,拉低数据总线

3.数据允许变化:在时钟总线低电平时

4.数据保持稳定,采样数据:在时钟总线高电平时

5.停止条件:时钟总线高电平时,拉高数据总线

6.ACK:应答是低电平有效,应答由接收方传出

三.24AA04/24LC04B如何通过I2C协议与主机进行通信

该eeprom的设备地址:1010

1.写入EEPROM(字节写/页写)

(1) 字节写

每一bit都需要一个sclk周期完成

控制字节

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-Fc0A9fnC-1642921692513)(C:UsersDELLDesktopRevisionProtocol_Verilogi2c_eepromdoc部分图image-20220117215006419.png)]

(2)页写

2. 读取EEPROM的数据(当前地址读/随机读/顺序读)

(1).当前地址读

(2).随机读,顺序读

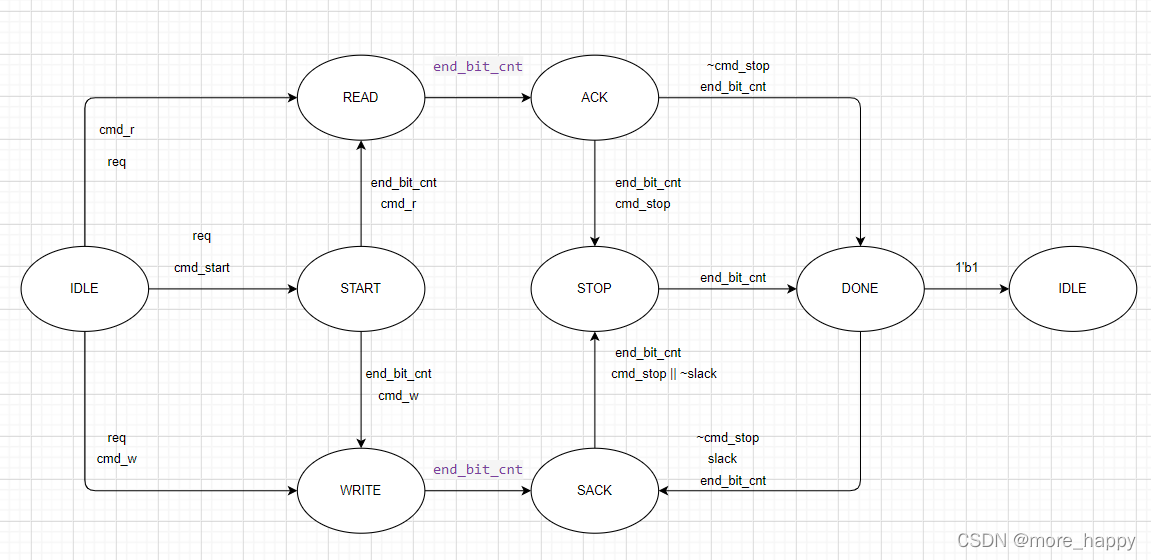

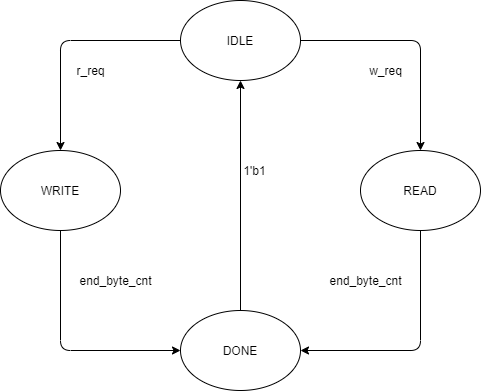

四. 状态转移图以及代码

1.I2C接口(驱动)模块

(1).状态图

(2).接口代码

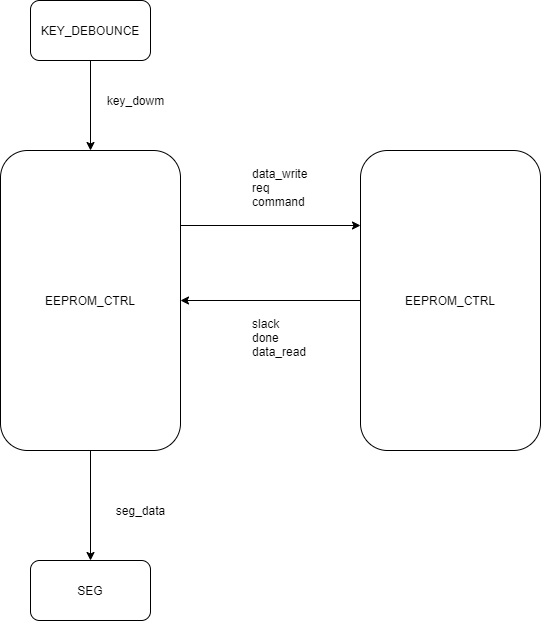

2. I2C控制模块

(1).状态图

(2).控制模块代码模块

3.TOP顶层模块

(1).整体框架

(2).代码

本文由 在线网速测试 整理编辑,转载请注明出处。