【FPGA的基础学习-----EEPROM读写测试】

- EEPROM简介

- EEPROM(AT24C64)

- IIC通讯协议

- 空闲状态

- 起始信号与停止信号

- 数据有效性

- 应答信号ACK

- 数据的传送

- AT24C64 单写时间序列

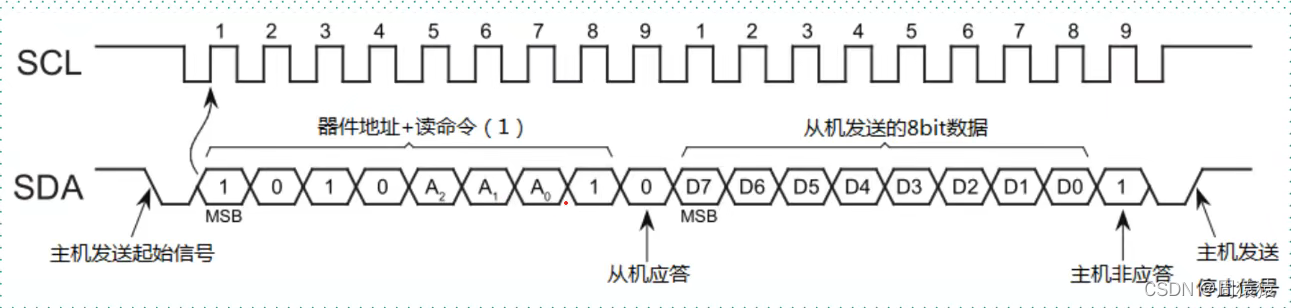

- AT24C64 当前地址读取时间

- 随机读取时间顺序 AAT24C64

最后更新:2022-04-06 06:07:12 手机定位技术交流文章

FPGA 基本知识-EEPROM 阅读和写作考试

EEPROM简介

EEPROM,即电子可移动程序只读存储器,是一种广泛使用的非损耗性内存(数据在断电时不会丢失 ) 。 不同类型的植物的不同类型和系列产品的寿命各不相同,有100万个典型的主流产品。

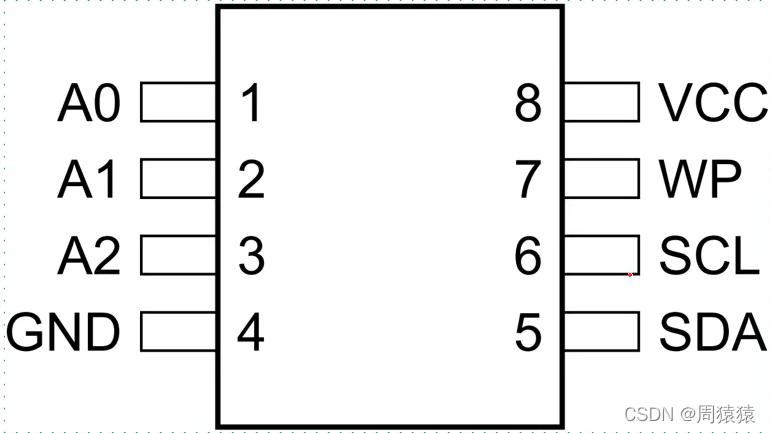

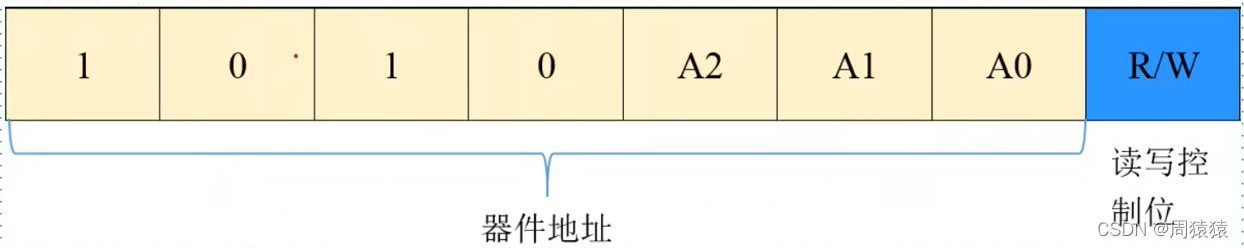

EEPROM(AT24C64)

内部分为256页,每页32字节,总容量为8 k(64k/8)。

FPGA 开发板上的硬硬件配置为 A0 = A1 = A2 = 0。 读写控制空格( 0: 写入 1 : 读)

IIC通讯协议

集成电路公交车(IIC)是PHLIPS设计的两线连环公交车,用于连接微控制器及其外围,大部分用于主机和机器的主要通信,但数据很少,传输时间很短。

IIC大客车由数据线路SDA和时钟线路SCI组成,可用于发送和接收数据。

100kbit/s是标准模型。

400kbit/s 快速模式

3.4米比特/秒高速模式

IIC是一种半功能通信模式。

空闲状态

IIC总线的两个信号线,即SDA和SCL,同时处于高高度,并被定性为公共汽车自由度。目前,每个装置的输出级现场效应管处于封闭状态,即公交线释放,两条信号线的每个线路都推高了电板。

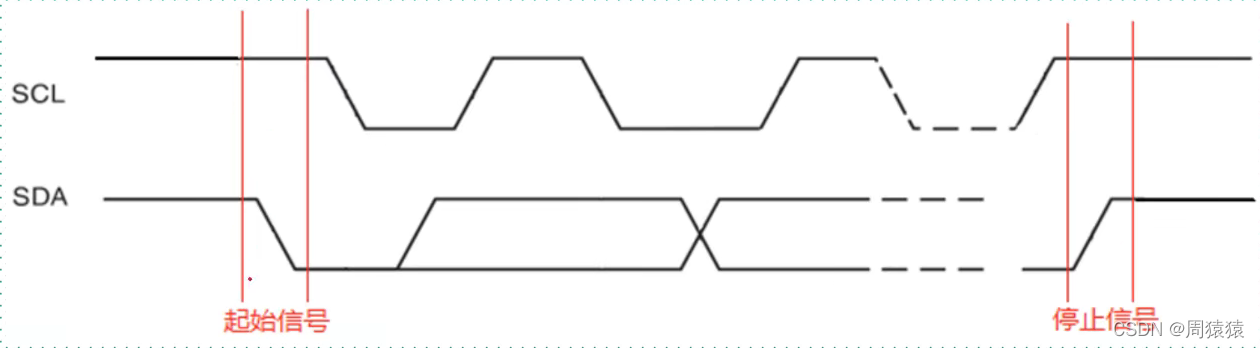

起始信号与停止信号

当信号启动时,自失能系统从高向低向低;向时间序列的平跳信号,而不是平的信号。

当短链氯化石蜡高时,自失能装置会从低到高;停止信号同样是一个电级跳至时序信号,而不是电级信号。

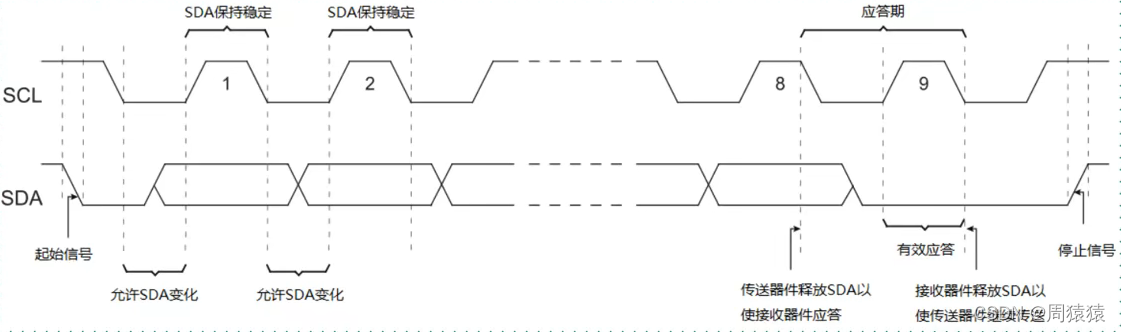

数据有效性

虽然国际电算公司总线传输数据,但时钟信号是高水平的,数据线数据必须保持稳定,只有在时钟信号是低水平时才允许改变数据线的高级别或低级别状态。

也就是说,在SCL上升之前必须准备好数据,在下降之前必须稳定。

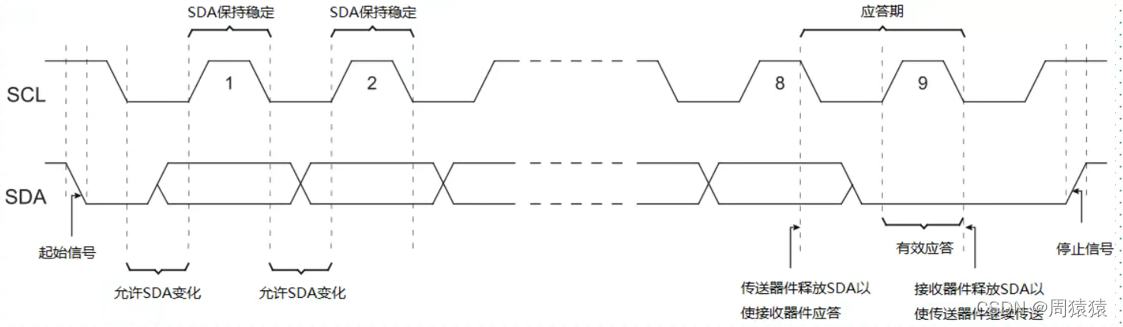

应答信号ACK

发件人发送一个字节。数据总线仅在9时钟脉冲9时才放行。接收器发出回信信号当响应信号在振幅上低时,有效反应位置的定义是ACK反应位置。这表明字节已被接收者成功确认;当回答信号为高空时,它被称为“无反应位置”(NACK)。它通常表明收受方没有成功收到字节。

为了使反馈能适当回应ACK的要求,在9时钟脉冲前的低水平期间,接收器拉下自失能线。保持时钟高水平的 持续低功率如果主控制是接收器,在收到最后字节后,它能够弄清楚发生了什么事情。发送NACK信号信息是通过提醒推定发送人来传播的。并释放SDA线,因此,主接收器将发送一个截停信号P

数据的传送

IIC总线上传输的每个数据位元包含一个时钟脉冲(或同步控制),其中每个数据位在SDA上相继传输,与SSL集群时钟相结合。数据位传输是一个在IIC总线上传输的边界触发点(或同步控制)包含一个时钟脉冲(或同步控制),其中每个数据位在SDA上相继传输,与SSL集群时钟结合。数据位传输是一个边界触发点。

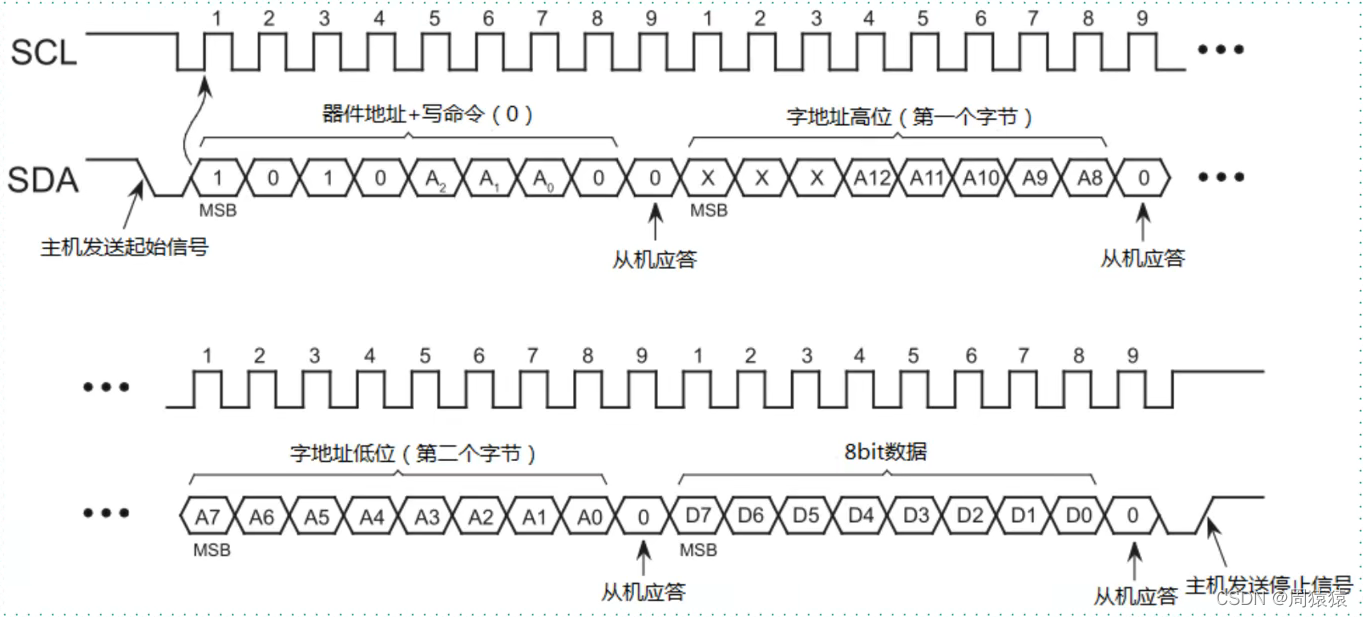

AT24C64 单写时间序列

写操作的时候,先要确定写的地址,所以要写器件地址->写地址->写data

AT24C64 当前地址读取时间

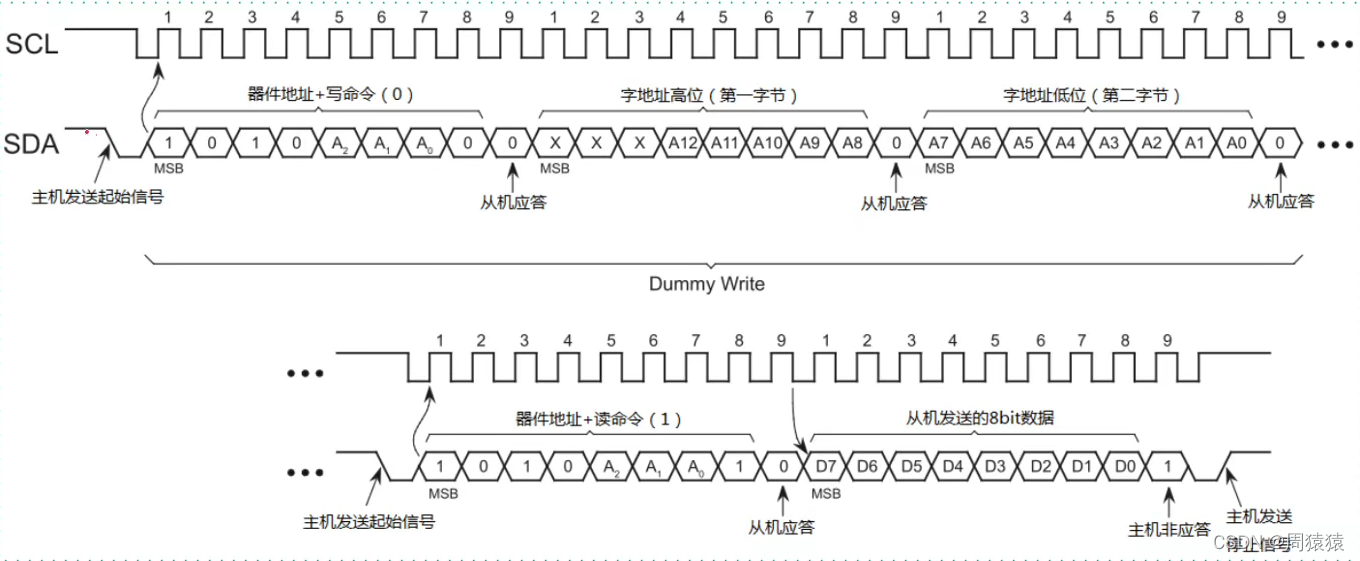

随机读取时间顺序 AAT24C64

在阅读操作前,您必须先找到读物的地址如下:

写模式->写读的地址->读模式->读数据

本文由 在线网速测试 整理编辑,转载请注明出处。